8 enhanced synchronous serial interface 0, Enhanced synchronous serial interface 0 -22, 8 enhanced synchronous serial interface 0 – Motorola DSP56301 User Manual

Page 52

Enhanced Synchronous Serial Interface 0

2

-22

DSP56301 User’s Manual

2.8

Enhanced Synchronous Serial Interface 0

Two synchronous serial interfaces (ESSI0 and ESSI1) provide a full-duplex serial port for

serial communication with a variety of serial devices, including one or more

industry-standard CODECs, other DSPs, microprocessors, and peripherals that implement the

Motorola serial peripheral interface (SPI). All ESSI pins are 5V tolerant.

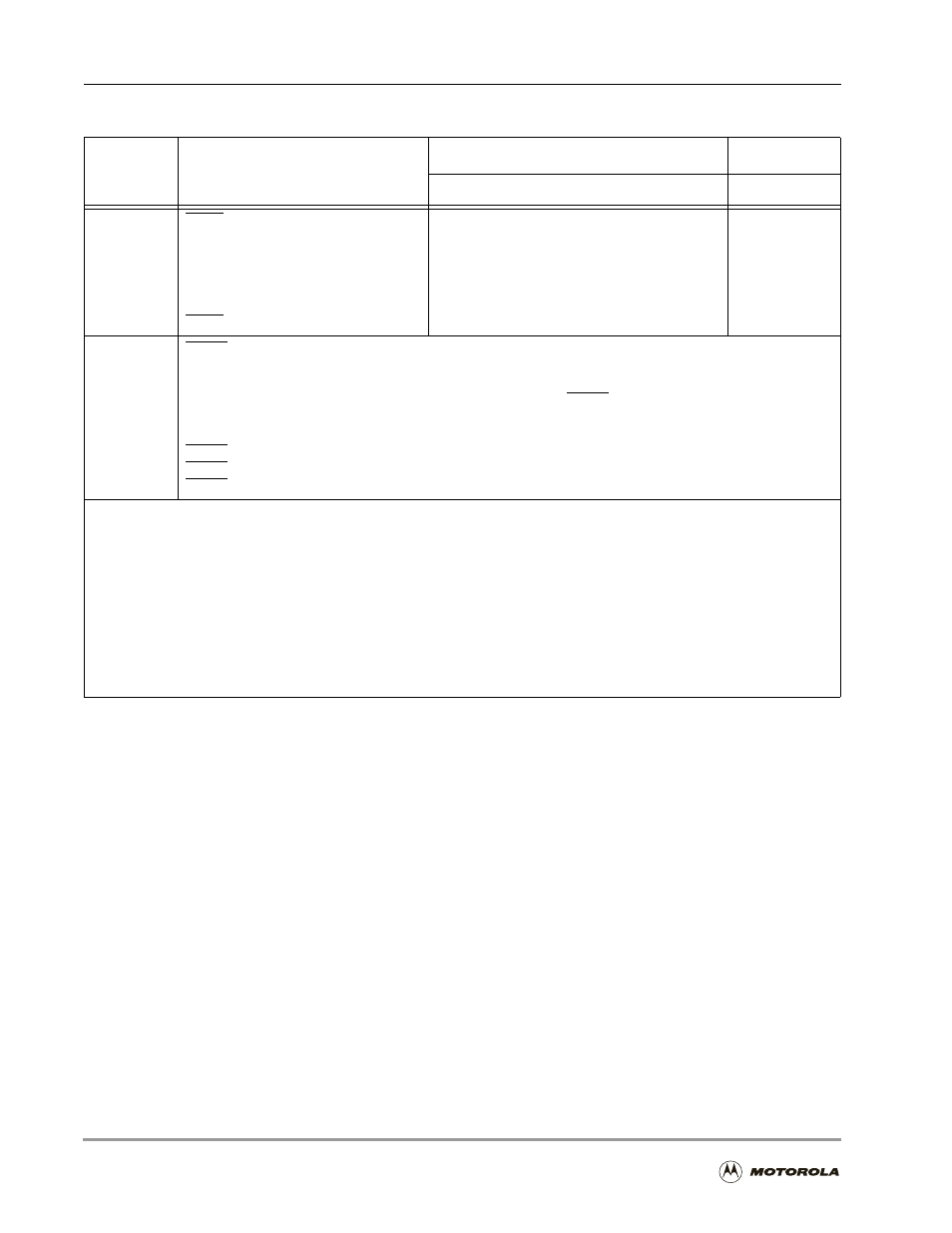

HP49

HRST

Hardware Reset

Input pin.

Forces the HI32 PCI sequencer to the

initial state. All pins are forced to the

disconnected state.

HRST is asynchronous to HCLK.

HRST

Hardware Reset

Schmitt-trigger input pin.

Forces the HI32 to its initial state. All pins are

forced to the disconnected state. The polarity

of the HRST pin is controlled by HRSP bit in

the DCTR.

HP50

HINTA

Host Interrupt A

Active low, open drain output pin

.

Used by the HI32 to request service from the host processor. HINTA can connect to an interrupt request

pin of a host processor, a control input of external circuitry, or be used as a general-purpose open-drain

output.

HINTA is asserted by the HI32 when the DSP56300 core sets DCTR[HINT].

HINTA is released (high impedance) when the DSP56300 core clears DCTR[HINT].

HINTA is asynchronous to HCLK.

Notes: 1.

This list does not include V

CC

and Ground supply pins.

2.

The GPIO pin is controlled by the corresponding bits in the GPIO data (DATH) and GPIO direction (DIRH)

registers.

3.

Open-drain output pin is driven, when asserted, by the HI32. When deasserted the pin is released (high

impedance). This enables using a multi-slave configuration. An external pull-up must connect externally for

proper operation.

4.

Sustained Tri-State is an active low tri-state signal owned and driven by one and only one agent at a time.

The agent that drives this pin low must drive it high for at least one clock before letting it float. A new agent

cannot start driving a sustained tri-state signal any sooner that one clock after the previous owner tri-states

it. A pull-up resistor is required to sustain the inactive state until another agent drives it.

5.

All pins except PCVL are 5 V tolerant.

Table 2-12. Host Port Pins (HI32) (Continued)

Signal

Name

PCI

Universal Bus Mode

Enhanced Universal Bus Mode

GPIO