2 dsp pci control register (dpcr), Dsp pci control register (dpcr) -26, 2 dsp pci control register (dpcr) – Motorola DSP56301 User Manual

Page 144

HI32 DSP-Side Programming Model

6

-26

DSP56301 User’s Manual

6.7.2

DSP PCI Control Register (DPCR)

The DPCR is a 24-bit read/write control register by which the DSP56300 core controls the

HI32 PCI interrupts and interface logic. The host processor cannot access the DPCR. The bit

manipulation instructions are useful for accessing individual bits in the DPCR.

.

5–3

HF[5–3]

0

UB/PCI Host Flags

General-purpose flags for DSP-to-host communication. The DSP56300

core can set or clear these bits. HF[5–3] are visible to the external host

in the HSTR. There are six host flags: three by which the host signals

the DSP56300 core (HF[2–0]) and three by which the DSP56300 core

signals the host processor (HF[5–3]). The host flags do not cause

interrupts; they must be polled to determine whether they have

changed. These flags can be used individually or as encoded triads.

2

SRIE

0

UB/PCI

Slave Receive Interrupt Enable

Enables a DSP56300 core interrupt request when the slave receive

data request (SRRQ) status bit in the DSR is set. When SRIE is

cleared, SRRQ interrupt requests are disabled. When SRIE is set, a

slave receive data interrupt request is generated if SRRQ is set.

1

STIE

0

UB/PCI Slave Transmit Interrupt Enable

Enables a DSP56300 core interrupt request when the slave transmit

data request (STRQ) status bit in the DSR is set. When STIE is cleared,

STRQ interrupt requests are disabled. When STIE is set, a slave

transmit data interrupt request is generated if STRQ is set.

0

HCIE

0

UB/PCI

Host Command Interrupt Enable

Enables a vectored core interrupt request when the DSR[HCP] is set.

When HCIE is cleared, HCP interrupt requests are disabled. When

HCIE and DSR[HCP] are both set, a host command interrupt request is

generated. The starting address of this interrupt is determined by the

host vector HV[6–0] in the Host Command Vector Register (HCVR).

When the host non-maskable interrupt (HNMI) bit is set in the Host

Command Vector Register (HCVR), HCIE is ignored, and an interrupt is

generated if HCP is set, regardless of HCIE.

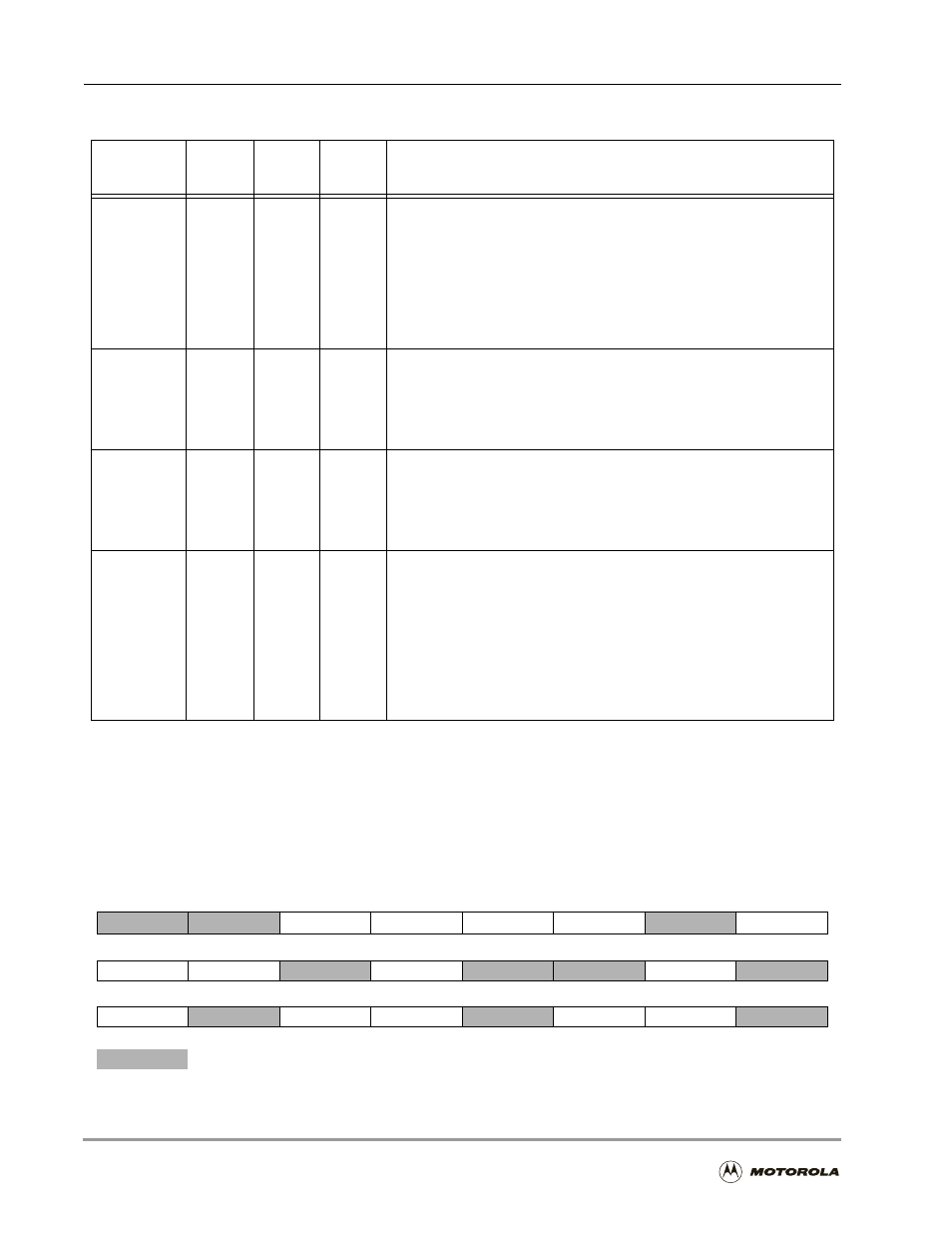

23

22

21

20

19

18

17

16

IAE

RBLE

MWSD

MACE

SERF

15

14

13

12

11

10

9

8

MTT

CLRT

TCIE

TTIE

7

6

5

4

3

2

1

0

TAIE

PEIE

MAIE

MRIE

MTIE

Reserved. Write to 0 for future compatibility

Figure 6-6. DSP PCI Control Register (DPCR)

Table 6-10. DSP Control Register (DCTR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset

Value

Mode

Description