Chapter 3, Board layout – Lanner LEC-3012 User Manual

Page 16

16

Board Layout

Chapter 3

Embedded and Industrial Computing

PIN

Description

PIN

Description

9

OE#

34

IOR#

10

A9

35

IOW#

11

A8

36

WE#

12

A7

37

READY#

13

CFVCC3

38

CFVCC3

14

A6

39

CSEL

15

A5

40

VS2#

16

A4

41

RESET

17

A3

42

WAIT#

18

A2

43

INPACK#

19

A1

44

REG#

20

A0

45

DASP#

21

DATA0

46

DIAG#

22

DATA1

47

DATA8

23

DATA2

48

DATA9

24

WP

49

DATA10

25

CD2-

50

GND

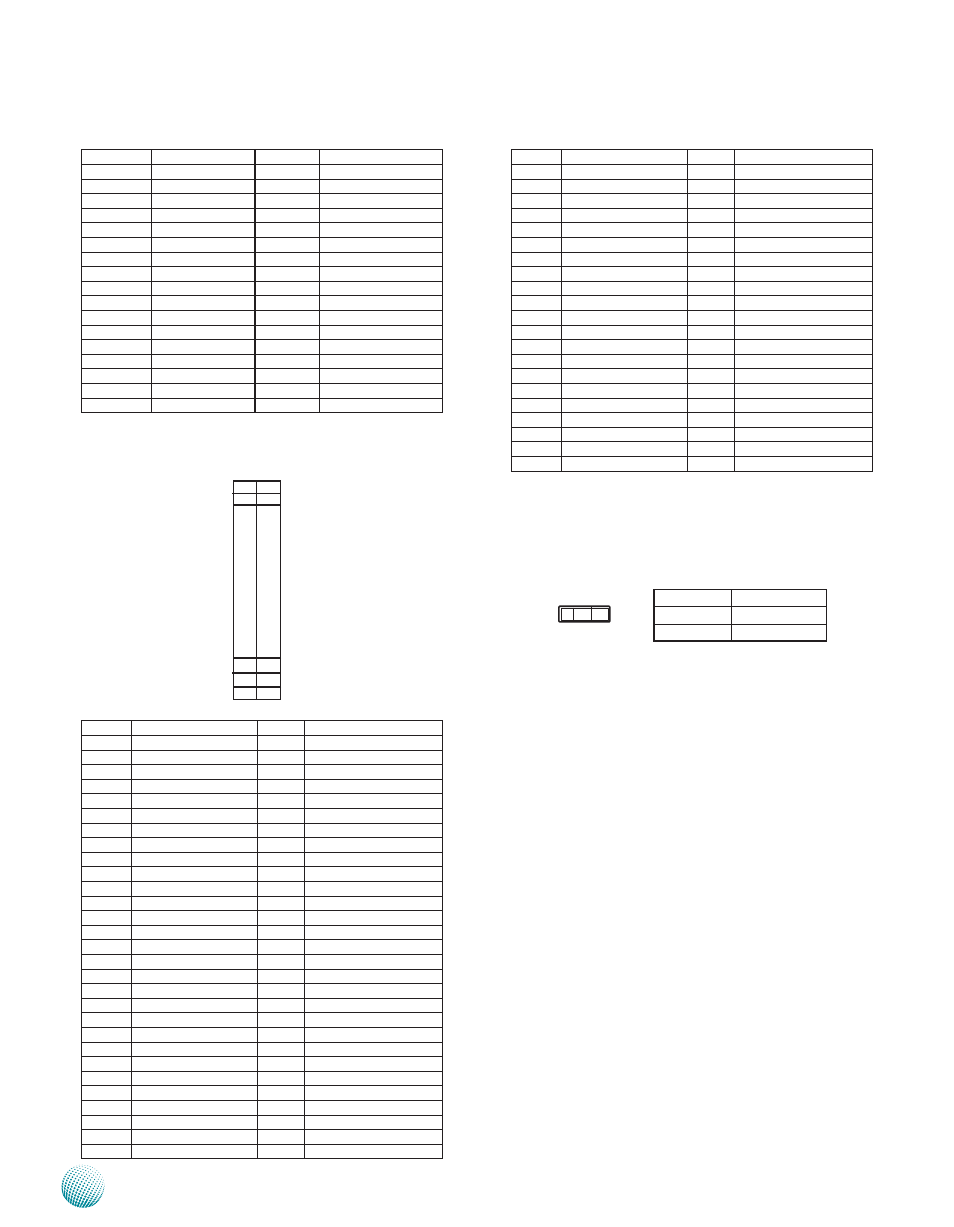

Board to Board Connector (J6)

PIN

Description

PIN

Description

1

PLTRST_BUF1_N

51

COM4_RXD

2

SMBCLK_MAIN

52

COM4_TXD

3

SMBDAT_MAIN

53

COM4_RTS#

4

HD_LED_N

54

COM4_CTS#

5

STATUS_GRN#

55

COM3_RXD

6

STATUS_RED#

56

COM3_TXD

7

SYS_PWROK_100MS

57

COM3_RTS#

8

COM5_DSR#

58

COM3_CTS#

9

COM5_DTR#

59

COM2_RXD

10

COM5_RI#

60

COM2_TXD

11

COM5_DCD#

61

COM2_RTS#

12

COM5_RXD

62

COM2_CTS#

13

COM5_TXD

63

COM1_RXD

14

COM5_RTS#

64

COM1_TXD

15

COM5_CTS#

65

COM1_RTS#

16

GND

66

COM1_CTS#

17

USBP_N3

67

GND

18

USBP_P3

68

SATA_TX_N2

19

GND

69

SATA_TX_P2

20

USBP_N2

70

GND

21

USBP_P2

71

SATA_RX_N2

22

GND

72

SATA_RX_P2

23

CLK_LAN6_100M_N

73

GND

24

CLK_LAN6_100M_P

74

CLK_LAN4_100M

25

GND

75

CLK_LAN4_100M

26

PCIE_TX_N6

76

GND

27

PCIE_TX_P6

77

PCIE_TX_N4

28

GND

78

PCIE_TX_P4

29

PCIE_RX_N6

79

GND

PIN

Description

PIN

Description

30

PCIE_RX_P6

80

PCIE_RX_N4

31

GND

81

PCIE_RX_P4

32

CLK_LAN5_100M

82

GND

33

CLK_LAN5_100M

83

CLK_LAN3_100M

34

GND

84

CLK_LAN3_100M

35

ICH_C_PCIE_TX

85

GND

36

ICH_C_PCIE_TX

86

PCIE_TX_N3

37

GND

87

PCIE_TX_P3

38

ICH_C_PCIE_RX

88

GND

39

ICH_C_PCIE_RX

89

PCIE_RX_N3

40

GND

90

PCIE_RX_P3

41

NC

91

GND

42

VCC3P3_PS

92

GND

43

VCC3P3_PS

93

GND

44

NC

94

GND

45

VCC5_PS

95

GND

46

VCC5_PS

96

GND

47

VCC5_PS

97

GPIO8_LEGACY

48

NC

98

GPIO7_LCD_PID1

49

VCC12_PS

99

GPIO6_LCD_PID0

50

VCC12_PS

100

GPIO1_TACH1

Clear CMOS jumper (JP1): It is for clearing the CMOS

memory.

50

1

100

51

Pin No.

Pin Name

1-2

Normal (Default)

2-3

Clear CMOS

1 2 3