Chapter 3 – DFI CD905-B2800 User Manual

Page 18

www.dfi .com

Chapter 3 Hardware Installation

18

Chapter 3

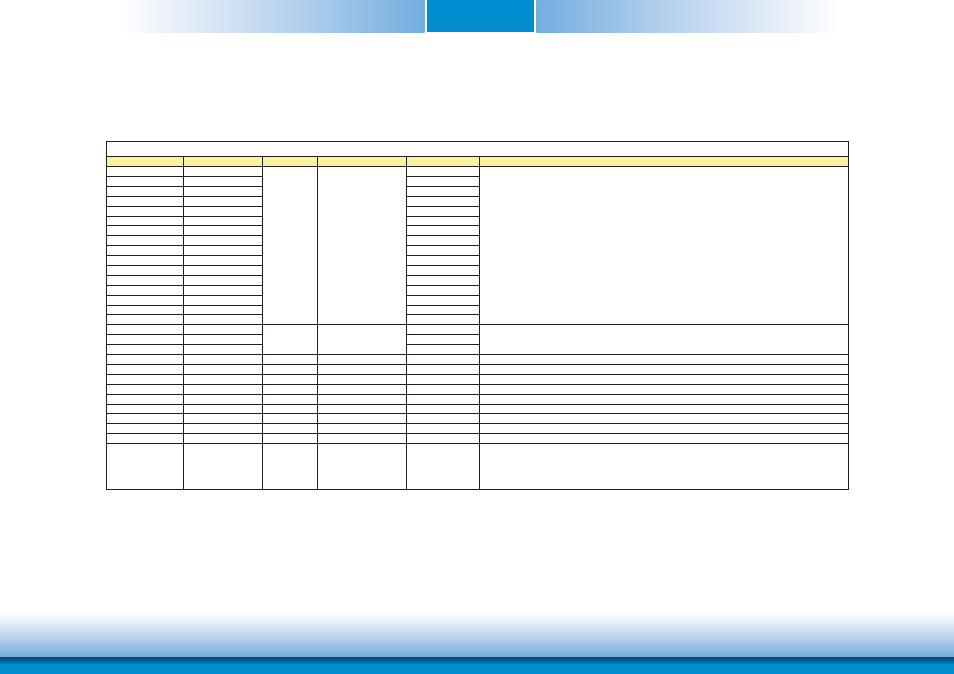

Signal

Pin#

Pin Type

Pwr Rail /Tolerance

PU/PD

Description

IDE_D0

D7

IDE_D1

C10

IDE_D2

C8

IDE_D3

C4

IDE_D4

D6

IDE_D5

D2

IDE_D6

C3

IDE_D7

C2

PD 10K

IDE_D8

C6

IDE_D9

C7

IDE_D10

D3

IDE_D11

D4

IDE_D12

D5

IDE_D13

C9

IDE_D14

C12

IDE_D15

C5

IDE_A0

D13

IDE_A1

D14

IDE_A2

D15

IDE_IOW#

D9

O CMOS

3.3V / 3.3V

I/O write line to IDE device. Data latched on trailing (rising) edge.

IDE_IOR#

C14

O CMOS

3.3V / 3.3V

I/O read line to IDE device.

IDE_REQ

D8

I CMOS

3.3V / 5V

PD 5.6K

IDE Device DMA Request. It is asserted by the IDE device to request a data transfer.

IDE_ACK#

D10

O CMOS

3.3V / 3.3V

IDE Device DMA Acknowledge.

IDE_CS1#

D16

O CMOS

3.3V / 3.3V

IDE Device Chip Select for 1F0h to 1FFh range.

IDE_CS3#

D17

O CMOS

3.3V / 3.3V

IDE Device Chip Select for 3F0h to 3FFh range.

IDE_IORDY

C13

I CMOS

3.3V / 5V

PU 4.7k to 3.3V

IDE device I/O ready input. Pulled low by the IDE device to extend the cycle.

IDE_RESET#

D18

O CMOS

5V

PU10k to 5V

Reset output to IDE device, active low.

IDE_IRQ

D12

I CMOS

3.3V / 5V

PD 10K

Interrupt request from IDE device.

IDE_CBLID#

D77

I CMOS

3.3V / 5V

PD 10K

Input from off-Module hardware indicating the type of IDE cable being

used. High indicates a 40-pin cable used for legacy IDE modes. Low

indicates that an 80-pin cable with interleaved grounds is used. Such a

cable is required for Ultra-DMA 66, 100 and 133 modes.

IDE Signals Descriptions

I/O CMOS

3.3V / 5V

Bidirectional data to / from IDE device.

O CMOS

3.3V / 3.3V

Address lines to IDE device.