Power and communication interfaces, External interface headers jp1 and jp2 – Zilog Z8F0880 User Manual

Page 13

Z8 Encore! XP

®

F1680 28-Pin Series Development Kit

User Manual

UM020305-0508

F1680 28-Pin Series Development Board

9

•

2.7 V to 3.6 V operating voltage with 5 V-tolerant inputs

•

Operating temperatures: 20° ±10° C

For more information on the Z8 Encore! XP

®

family of devices, refer to

Z8 Encore! XP

®

F1680 Series Product Specification (PS0250), available

for download at

www.zilog.com

.

Power and Communication Interfaces

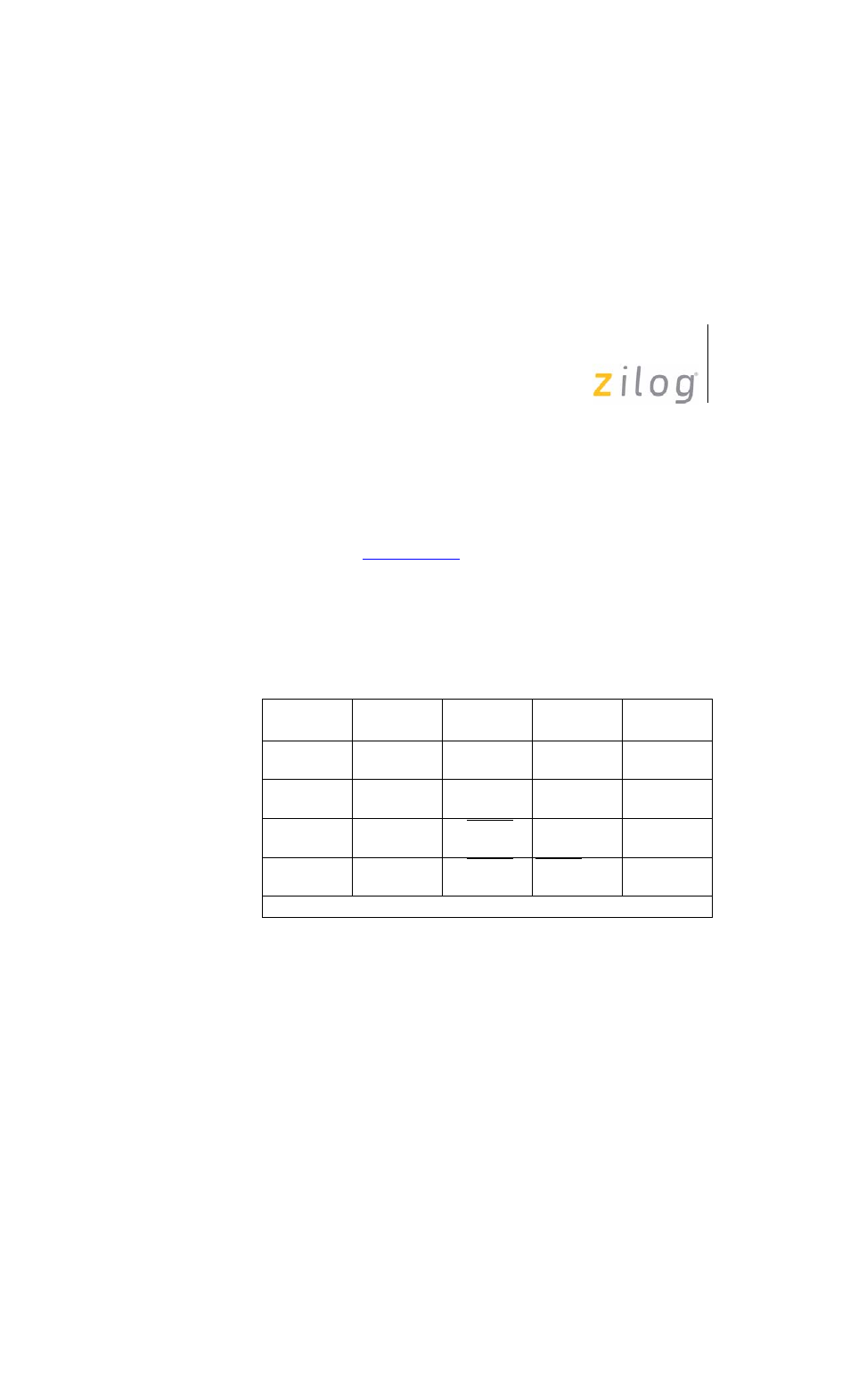

Table 1

provides jumper information concerning the shunt status,

functions, devices and defaults affected by jumpers JP3 and JP4.

External Interface Headers JP1 and JP2

External interface headers JP1 and JP2 are shown in the schematic on

page 13.

Table 1. Jumpers JP3 and JP4

Jumper

Status

Device

Affected

Status

Default

JP3*

OUT

RS-232

interface

Enabled

X

JP3

IN

RS-232

interface

Disabled

JP5

OUT

U5 RESET/

PD0

PD0 (GPIO)

X

JP5

IN

U5 RESET/

PD0

RESET when

SW1 pressed

Note: * These jumpers must not be OUT at the same time.