Connect Tech BLUE HEAT/NET SYNC CTIM-00044 User Manual

Page 53

Connect Tech Blue Heat/Net Sync User Manual

Revision 0.03

53

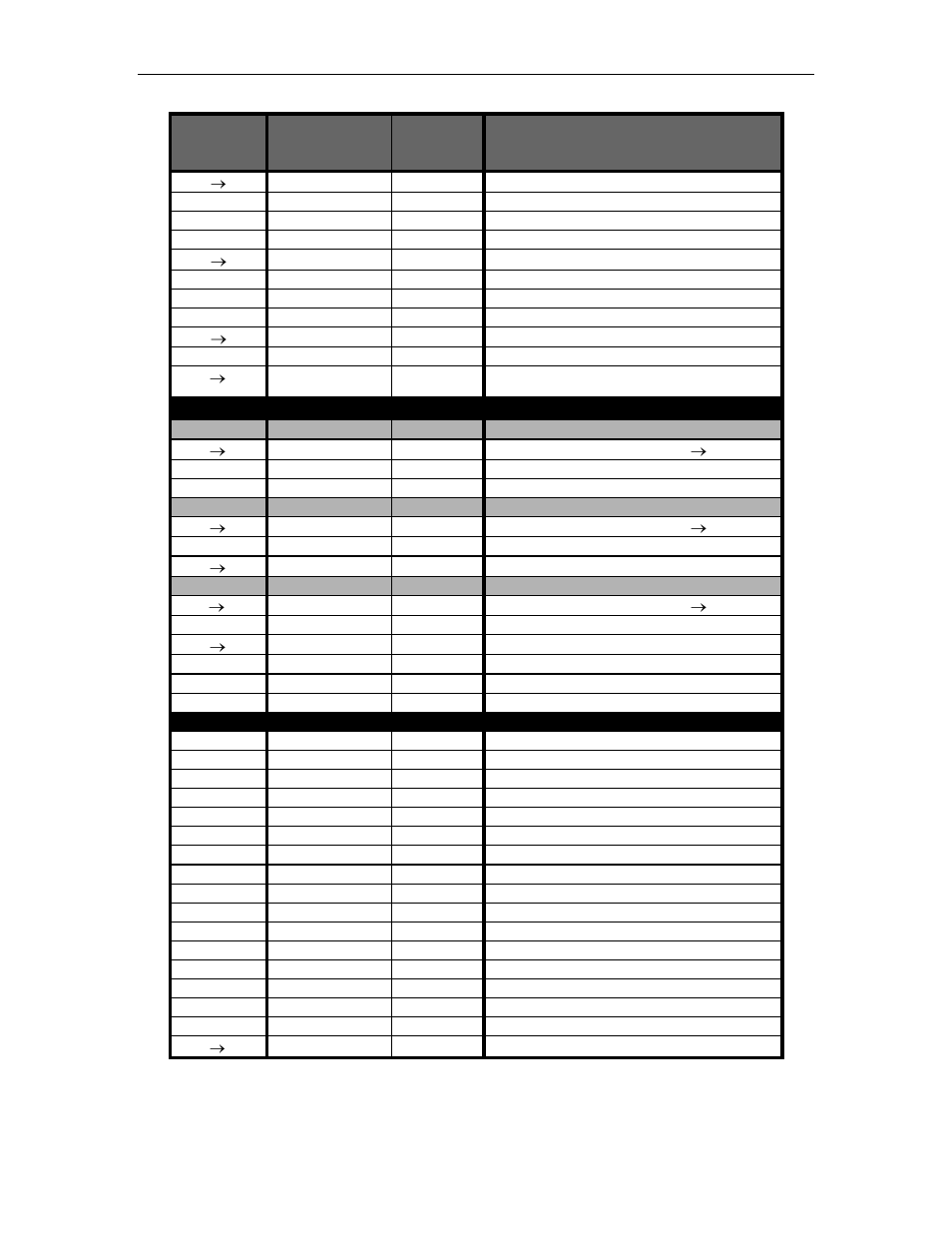

Address

Offset

(in hex)

Area (item)

Accessed

Register

Accessed

Notes

1A0

1A9

---

---

Reserved, do not access

1AA

IUSC-0 Dreg

RBCR

1AC

IUSC-0 Dreg

RARL

1AE

IUSC-0 Dreg

RARU

1B0

1B9

---

---

Reserved, do not access

1BA

IUSC-0 Dreg

NRBCR

1BC

IUSC-0 Dreg

NRARL

1BE

IUSC-0 Dreg

NRARU

1C0

1FF

---

---

Reserved, do not access

200

IUSC-0

Interrupt Acknowledge (read only)

202

3FF

IUSC-0

Aliases of 200

IUSC-1

400

5FF

IUSC-1

As Above

Same registers as addresses 000

1FF

600

IUSC-1

Interrupt Acknowledge (read only)

602-7FF

IUSC-1

Aliases of 600

IUSC-2

800

9FF

IUSC-2

As Above

Same registers as addresses 000

1FF

A00

IUSC-2

Interrupt Acknowledge (read only)

A02

BFF

IUSC-2

---

Aliases of A00

IUSC-3

C00

DFF

IUSC-3

As Above

Same registers as addresses 000

1FF

E00

IUSC-3

---

Interrupt Acknowledge (read only)

E02

FFF

IUSC-3

---

Aliases of E00

PLD Area

See “PLD Registers” for details.

1000

RTCU

Real Time Clock Upper

1002

RTCL

Real Time Clock Lower

1004

LEDC

LED Control

1006

Alias of 1004

1008

LIFC1

Port-1 Line I/F control

100A

Alias of 1008

100C

LIFC2

Port-2 Line I/F control

100E

Alias of 100C

1010

LIFC3

Port-3 Line I/F control

1012

Alias of 1010

1014

LIFC4

Port-4 Line I/F control

1016

Alias of 1014

1018

PLD_CNTRL

Control Bits

101A

Alias of 1018

101C

PLD_STATUS

Status bits

101E

Alias of 101C

1020

1FFF

Unused

[1] Sreg =

Serial Register

[2] Dreg =

DMA Register