Nd figure 22, Hsc-adc-evalc – Analog Devices HSC-ADC-EVALC User Manual

Page 25

HSC-ADC-EVALC

Rev. 0 | Page 25 of 32

D

C

B

A

D

C

B

A

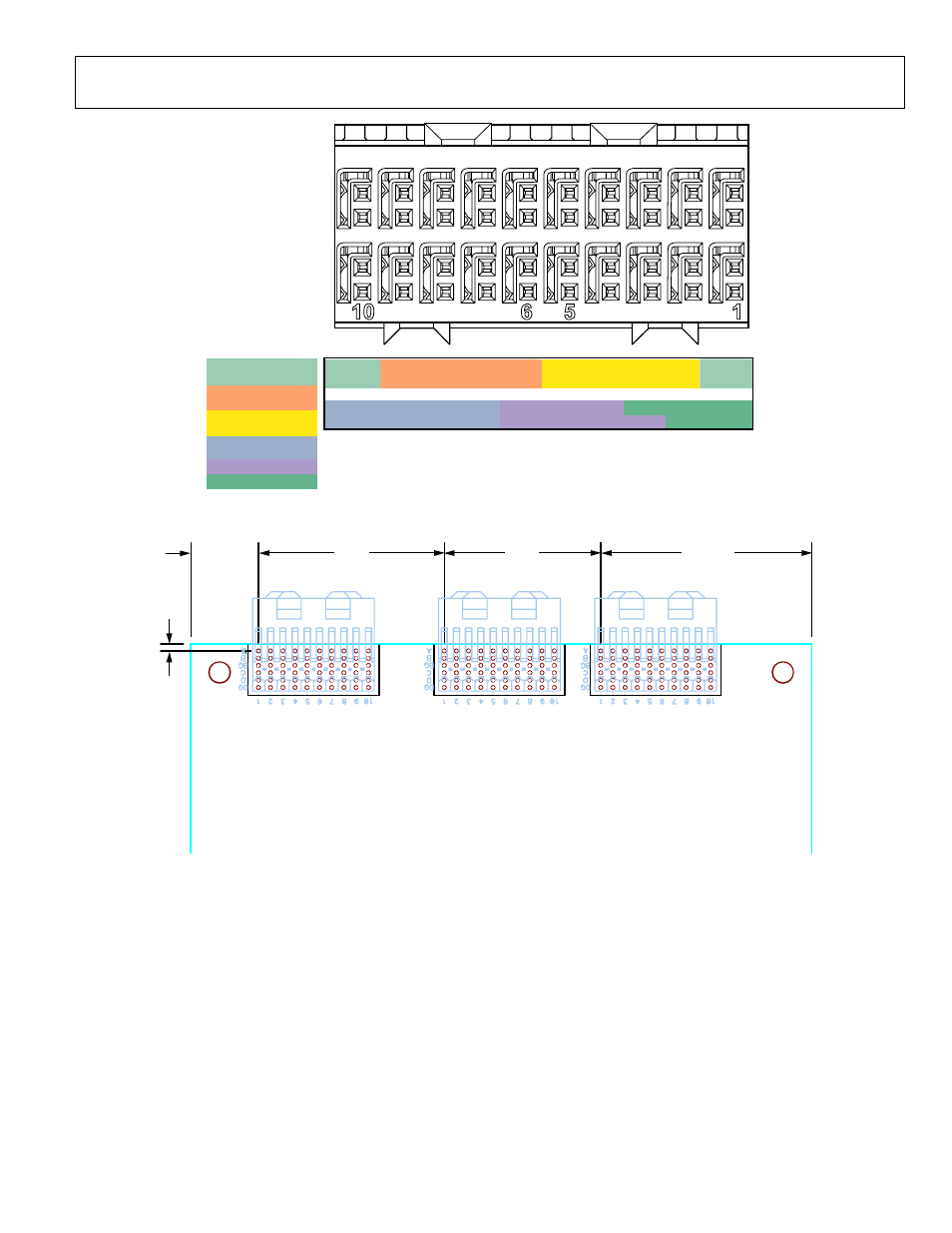

MGTCLK1– SD1–

SD2–

SD3–

SD4–

SD5–

SD6–

SD7–

SD8– MGTCLK2–

MGTCLK1+ SD1+

SD2+

SD3+

SD4+

SD5+

SD6+

SD7+

SD8+ MGTCLK2+

I/O_1

I/O_3

I/O_5

I/O_7

SCLK

SDI

SDO

USB_1

USB_2

USB_4

I/O_2

I/O_4

I/O_6

I/O_8

CSB_1

CSB_2

CSB_3

CSB_4

USB_3

USB_5

(J1) HS-SERIAL/SPI/AUX

HIGH SPEED SERIAL

REFERENCE CLK

HIGH SPEED SERIAL

DATA INPUTS

FUTURE HIGH SPEED

SERIAL DATA INPUTS

FPGA GENERAL

PURPOSE I/O

SPI CONTROL (3.3V)

USB DIRECT I/O (3.3V)

06

67

6-

02

2

Figure 22. J1 Pin Mapping

HS-SERIAL/SPI/AUX

J1

J2

DATA BUS 1

J3

DATA BUS 2

1.4mm

13.843mm

38mm

32mm

43.155mm

06

67

6-

02

3

Figure 23. Data Converter I/O Connector Placement (Top View)