System performance, Avr cpu and instruction set, Event system – Atmel AVR XMEGA 8/16-bit High Performance Low Power Flash Microcontrollers User Manual

Page 6

AVR XMEGA™ MiCROCOnTOLLERS

Everywhere You Are

®

System Performance

For Embedded systems, system performance is much more than a good MiPS number. it is important to

have powerful peripherals and features that allow the application to run smoothly with minimum power

consumption.

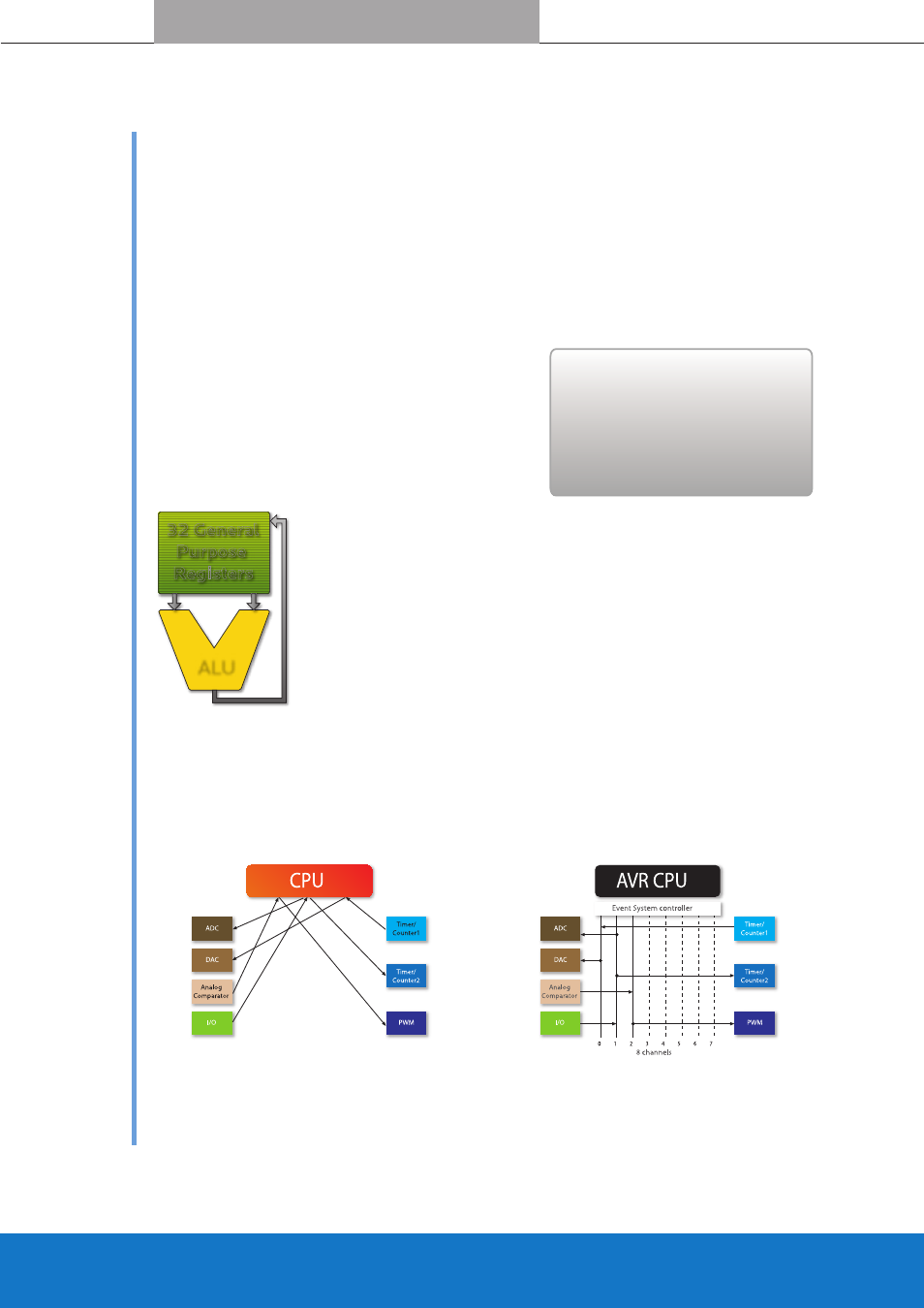

AVR CPU and instruction Set

The AVR XMEGA uses the AVR RiSC CPU which is

created for high level C code development. The instruc-

tion set and CPU design are tuned for minimum code size

and maximum execution speed. Due to the true single

cycle execution of arithmetic and logic operations, AVR

microcontrollers perform close to 1 MiPS per MHz.

Event System

The innovative AVR XMEGA Event System allow peripherals to send signals (events) directly to other peripherals

without involving the CPU. This ensures short and 100% predictable response time and at the same time

offloads the CPU.

ALU

32 General

Purpose

Registers

Central in the AVR architecture is the fast-access register file with 32 x 8-bit

general purpose working registers directly connected to the Arithmetic Logic

Unit. Within a single clock cycle the ALU can be fed two arbitrary registers, do a

requested operation, and write back the result.

The AVR XMEGA instruction set also support atomic 16-bit register access,

32-bit arithmetics, and have three 24-bit memory pointers.

Without Event System all Peripheral Requests need to be handled

by the CPU.

With Event System peripherals can send signals (events) to other

peripherals.

C Source:

unsigned char *var1, *var2;

*var1++ = *--var2;

Generated assembly code:

LD R16, -x

ST z+, R16

Auto increment/Decrement example