Extension to the 3dnow! instruction set, Prescott new instructions, A.6.7 extension to the 3dnow! instruction set – AMD SimNow Simulator 4.4.5 User Manual

Page 237: A.6.8 prescott new instructions, Amd confidential user manual november 21

AMD Confidential

User Manual

November 21

st

, 2008

Appendix A

225

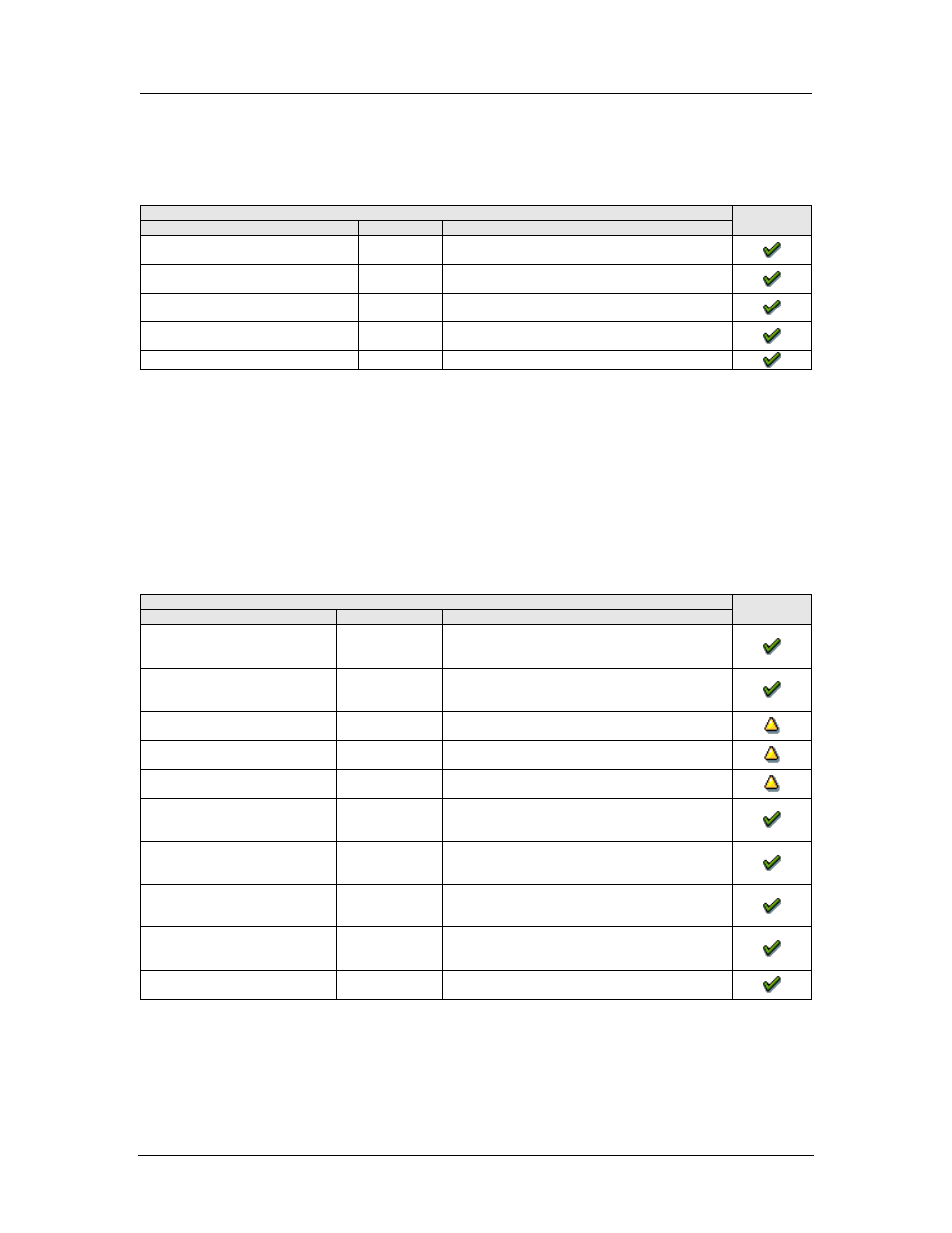

A.6.7 Extension to the 3DNow! Instruction Set

This section describes the five new DSP instructions added to the 3DNow! Instruction

set.

Instruction

Supported

Mnemonic

Opcode

Description

PF2IW mmreg1,mmreg2/m64

0F 0F /1C

Packed floating-point to integer

word conversion with sign extend.

PFNACC mmreg1,mmreg2/m64

0F 0F /8A

Packed

floating-point

negative

accumulate.

PFPNACC mmreg1,mmreg2/m64

0F 0F /8E

Packed

floating-point

mixed

positive-negative accumulate.

PI2FW mmreg1,mmreg2/m64

0F 0F /0C

Packed 16-bit integer to floating-

point conversion.

PSWAPD mmreg1,mmreg2/m64

0F 0F /BB Packed swap double word.

Table 15-11: Extension to 3DNow! Instruction Reference

A.6.8 Prescott New Instructions

Prescott New Instruction technology for the x64 architecture is a set of 13 new

instructions that accelerate performance of Streaming SIMD Extension technology,

Streaming SIMD Extension 2 technology, and x87-FP math capabilities. The new

technology is compatible with existing software and should run correctly, without

modification. The thirteen new instructions are summarized in the following section. For

detailed information on each instruction refer to a complete Instruction Set Reference.

Instruction

Supported

Mnemonic

Opcode

Description

ADDSUBPD xmm1,xmm2/m128

66 0F D0 /r

Add/Subtract packed double-precision

floating-point number from XMM2/Mem

to XMM1.

ADDSUBPS xmm1,xmm2/m128

F2 0F D0 /r

Add/Subtract packed single-precision

floating-point number from XMM2/Mem

to XMM1.

FISTTP m16int

DF /1

Store

ST

as

a

signed

integer

(truncate) in m16int and pop ST.

FISTTP m32int

DB /1

Store

ST

as

a

signed

integer

(truncate) in m32int and pop ST.

FISTTP m64int

DD /1

Store

ST

as

a

signed

integer

(truncate) in m16int and pop ST.

HADDPD xmm1,xmm2/m128

66 0F 7C /r

Add

horizontally

packed

double-

precision

floating-point

numbers

from XMM2/Mem to XMM1.

HADDPS xmm1,xmm2/m128

F2 0F 7C /r

Add

horizontally

packed

single-

precision

floating-point

numbers

from XMM2/Mem to XMM1.

HSUBPD xmm1,xmm2/m128

66 0F 7D /r

Subtract horizontally packed double-

precision

floating-point

numbers

from XMM2/Mem to XMM1.

HSUBPS xmm1,xmm2/m128

F2 0F 7D /r

Subtract horizontally packed single-

precision

floating-point

numbers

from XMM2/Mem to XMM1.

LDDQU xmm,m128

F2 0F F0 /r

Load 128 bits from Memory to XMM

register.