Silicon Motion SM2246 User Manual

Mobile storage, Sm2246, Zoom family

Mobile Storage

Zoom Family

www.siliconmotion.com

This publication, including all photographs, illustrations and software, is protected under

international copyright laws, with all rights reserved. Neither this publication, nor any of the

material contained herein, may be reproduced without written consent of the manufacturer.

© Copyright 2013 Silicon Motion, Inc.

SATA 6Gb/s Solid-State Drive Controller

SM2246

The SM2246 is a high-performance SATA 6Gb/s SSD

controller ideally suited for NAND-cache drives used

in low-cost and performance-enhancing hybrid

storage solutions for PCs, Ultrabooks tablets and

other embedded applications. Its ultra-low power

consumption effectively extends battery life and

optimizes user experience. The SM2246 fully

supports the latest generation MLC/TLC/SLC NAND

in high-speed Toggle, ONFI, and Async mode,

enabling the realization of cost-effective and highly

reliable SSDs on the market.

Flash Memory Support

Supports 4 channels of NAND flash devices with

up to 1 Chip Selects per channel

Supports 1.8V/3.3V Flash I/O

Supports ONFI 3.0 and Toggle 2.0 interface

EDO mode support

Supports 1x/1y/2x/2ynm MLC, TLC and SLC

Supports 8KB and 16KB page size

Supports 1-plane, 2-plane, and 4-plane operation

Operating Temperature

Commercial Grade: 0°C ~ 70°C

Package

288-ball TFBGA

Lead-free and RoHS compliant

Key Features

Host Interface

- Industrial Standard SATA Revision 3.1 compliant

- Industrial Standard ATA/ATAPI-8 and ACS2

command compliant

- Supports SATA interface rate of 6Gb/s

- Native Command Queuing up to 32 commands

- SATA Device Sleep (DevSleep)

- Data Set Management command (TRIM)

- Self-Monitoring, Analysis, and Reporting

Technology (S.M.A.R.T.)

- Supports PHY Sleep mode (CFast PHYSLP)

- Supports 28-bit and 48-bit LBA (Logical Block

Addressing) mode commands

DRAM Interface

- 16-bit wide DRAM interface

- Supports DDR2/DDR3/DDR3L

Data Protection and Reliability

- Supports ATA8 security feature set

- Supports data security erase and quick erase

- Configurable BCH ECC

- Internal data shaping increases data endurance

- Global wear leveling algorithm evens

program/erase count and maximizes SSD lifespan

- Software/Hardware write protect option

- StaticDataRefresh ensures data integrity

- Early weak block retirement option

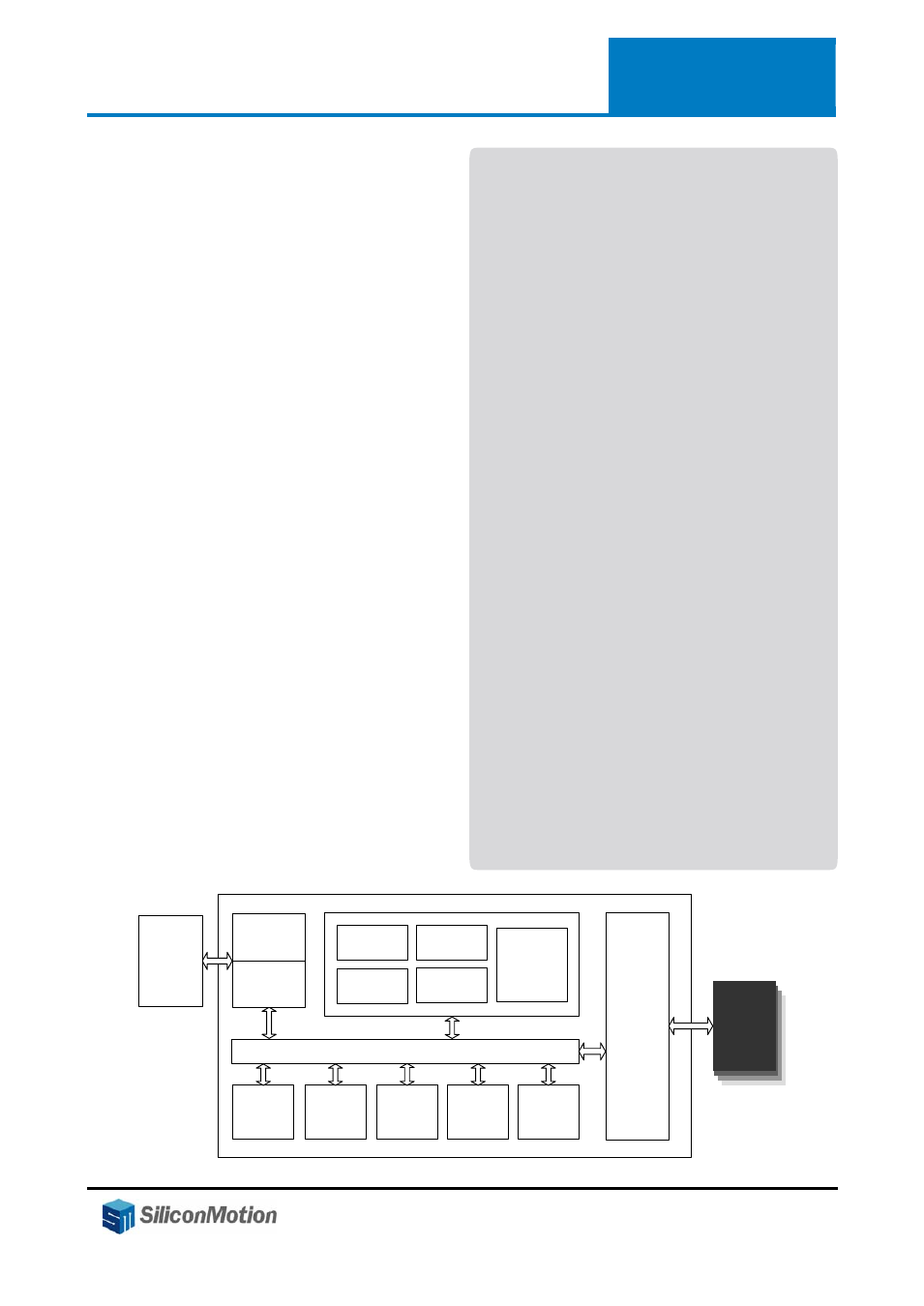

Architecture

- 32-bit RISC CPU

- High-efficiency 64-bit system bus

- Automatic sleep and wake-up mechanism to save

power

- Built-in voltage detectors for power failure

protection

- Built-in power-on reset and voltage regulators

- Built-in sensor for SSD temperature detection

- Supports JTAG emulator interface, bidirectional

UART (RS-232) interface, and I2C master/slave

interface for on-system debug

DRAM

Controller

Main

System

Buffer

DMA

Controller

ECC

Engine

UART

Interface

Flash

Controller

Bus Controller

NAND

Flash

Arrays

SATA MAC

SATA PHY

SPI Loader

Micro

Processor

Data

Cache

ROM

Instruction

Cache

SATA

Host