IEI Integration LVDS-VGA-R10 User Manual

Page 10

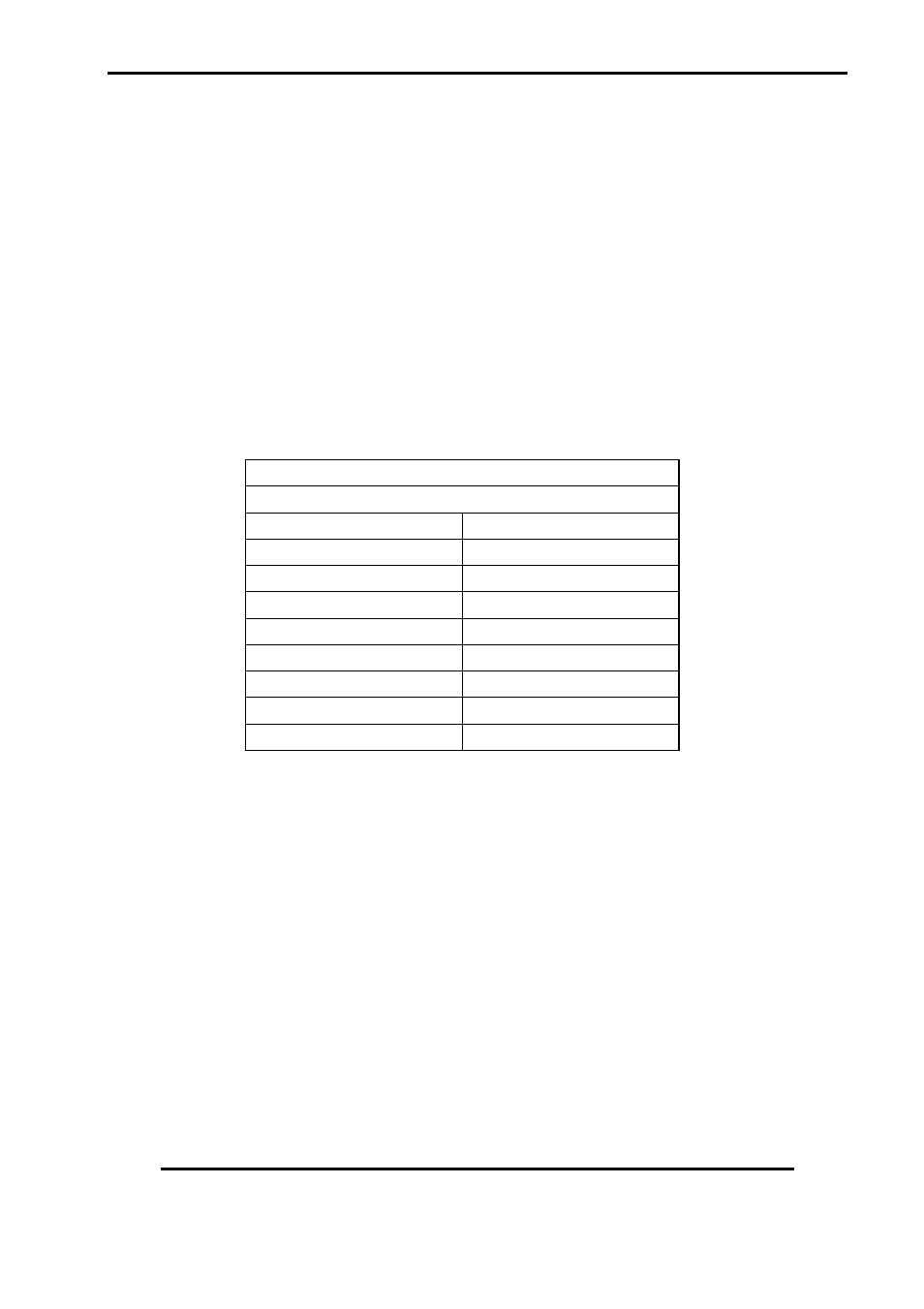

2.3.1 Interrupt Status Register Setup

(S1,Vector

Address)

When data arrives at one of the four ports, it will generate

an interruption in the interrupt register. The PC software

can read this, and identify immediately which port generated

the interruption. This saves time, and makes programming

easier. When a data bit of the interrupt status register is set

to 1, the corresponding channel is selected to generate an

interruption. If the bit is 0,then no interruption is generated.

S1 controls the interrupt status register for the card, as shown

in he following figure.

S1 300H (default)

10

Interrupt Status Register S1

Bit Function

0 Port

1

1 Port

2

2 Port

3

3 Port

4

4 Not

Used

5 Not

Used

6 Not

Used

7 Not

Used

- SPCIE-5100DX (180 pages)

- SPCIE-C2060 v1.01 (200 pages)

- SPCIE-C2060 v2.12 (212 pages)

- SPCIE-C2160 (204 pages)

- SPCIE-C2260-i2 (217 pages)

- ROCKY-3786 v4.0 (175 pages)

- ROCKY-3786 v4.10 (147 pages)

- PCIE-Q350 v1.00 (272 pages)

- PCIE-Q350 v1.12 (250 pages)

- PCIE-Q350 v1.20 (250 pages)

- PCIE-Q350 v1.30 (213 pages)

- PCIE-Q57A (159 pages)

- PCIE-G41A2 (151 pages)

- PCIE-Q670 v1.03 (206 pages)

- PCIE-Q670 v2.00 (205 pages)

- PCIE-H610 (181 pages)

- PCIE-Q870-i2 (217 pages)

- IOWA-LX-600 (159 pages)

- PCISA-945GSE v1.01 (207 pages)

- PCISA-945GSE v1.10 (190 pages)

- PCISA-9652 v1.00 (232 pages)

- PCISA-9652 v1.01 (232 pages)

- PCISA-PV-D4251_N4551_D5251 (145 pages)

- PICOe-945GSE (197 pages)

- PICOe-GM45A (198 pages)

- PICOe-PV-D4251_N4551_D5251 v1.00 (154 pages)

- PICOe-PV-D4251_N4551_D5251 v1.10 (154 pages)

- PICOe-PV-D4251_N4551_D5251 v1.11 (155 pages)

- PICOe-B650 (156 pages)

- PICOe-HM650 (174 pages)

- HYPER-KBN (139 pages)

- SPXE-14S (3 pages)

- SPXE-9S v1.00 (5 pages)

- SPXE-9S v1.1 (6 pages)

- SPE-9S v1.00 (4 pages)

- SPE-9S v1.1 (5 pages)

- SPE-6S (3 pages)

- SPE-4S (4 pages)

- PE-6SD3 (4 pages)

- PE-6SD2 v4.0 (4 pages)

- PE-6SD2 v2.10 (3 pages)

- PE-6SD (3 pages)

- PE-6S3 v1.0 (2 pages)

- PE-6S3 v4.0 (4 pages)

- PE-6S2 (4 pages)