AAEON AEC-6930 User Manual

Page 50

E m b e d d e d C o n t r o l l e r

A E C - 6 9 3 0

Appendix A Programming the Watchdog Timer A-3

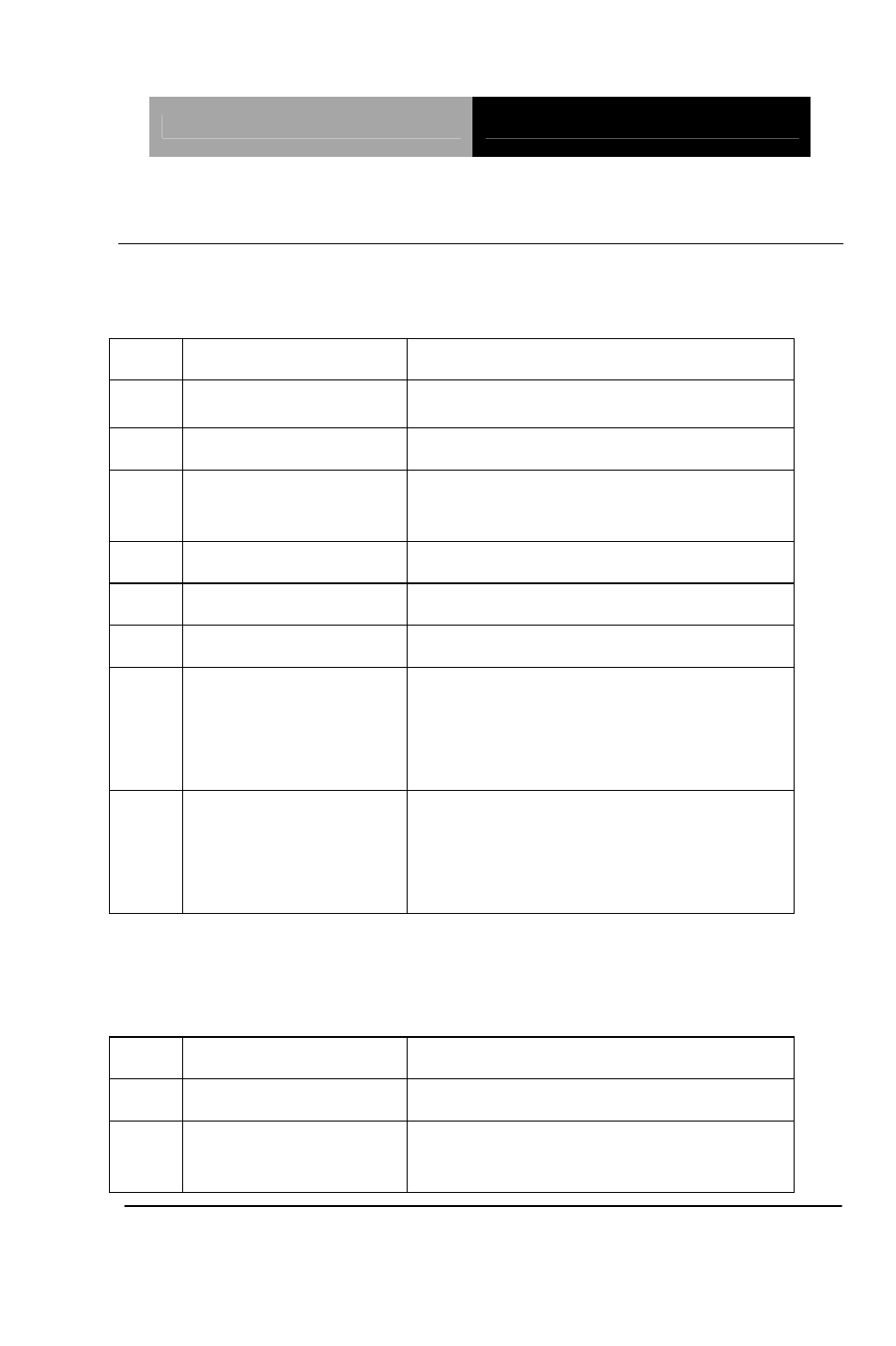

A.3 Registers Description

Configuration and Control Register – Index 01h

Power-on default [7:0] =0000_1000b

Bit Name

Description

7 INIT

Software reset for all registers including

Test Mode registers. Users use only.

6 Reserved

5 EN_WDT10

Enable Reset Out. If set to 1, enable

WDTOUT10# output. Default is

disable.

4 Reserved

3 Reserved

2 Reserved

1 SMART_POWR

_MANAGEMENT

Set this bit to 1 will enable auto power

down mode, when all function are idle

then 20ms the chip will auto power

down, it will wakeup when GPIO state

change or read write register

0 SOFT_POWR_

DOWN

Set this bit to 1 will power down all of the

analog block and stop internalclock,

write 0 to clear this bit or when GPIO

state change will auto clear

this bit to 0.

WDTOUT Control Register – Index 34h

Power-on default [7:0] =0000_0000b

Bit Name

Description

7-3 Reserved

2 SEL_RST_2S

When set this bit to 1, the WDTOUT10

low pulse width is 2 Sec, if set to 0 the

low pulse width is 100ms.