AAEON EMB-CV2 User Manual

Page 66

M i n i - I T X

E M B - C V 2

Appendix A Programming the Watchdog Timer

A-5

01h: Time-out occurs after 1 second/minute

02h: Time-out occurs after 2 second/minutes

03h: Time-out occurs after 3 second/minutes

…………………………………………………..

FFh: Time-out occurs after 255 second/minutes

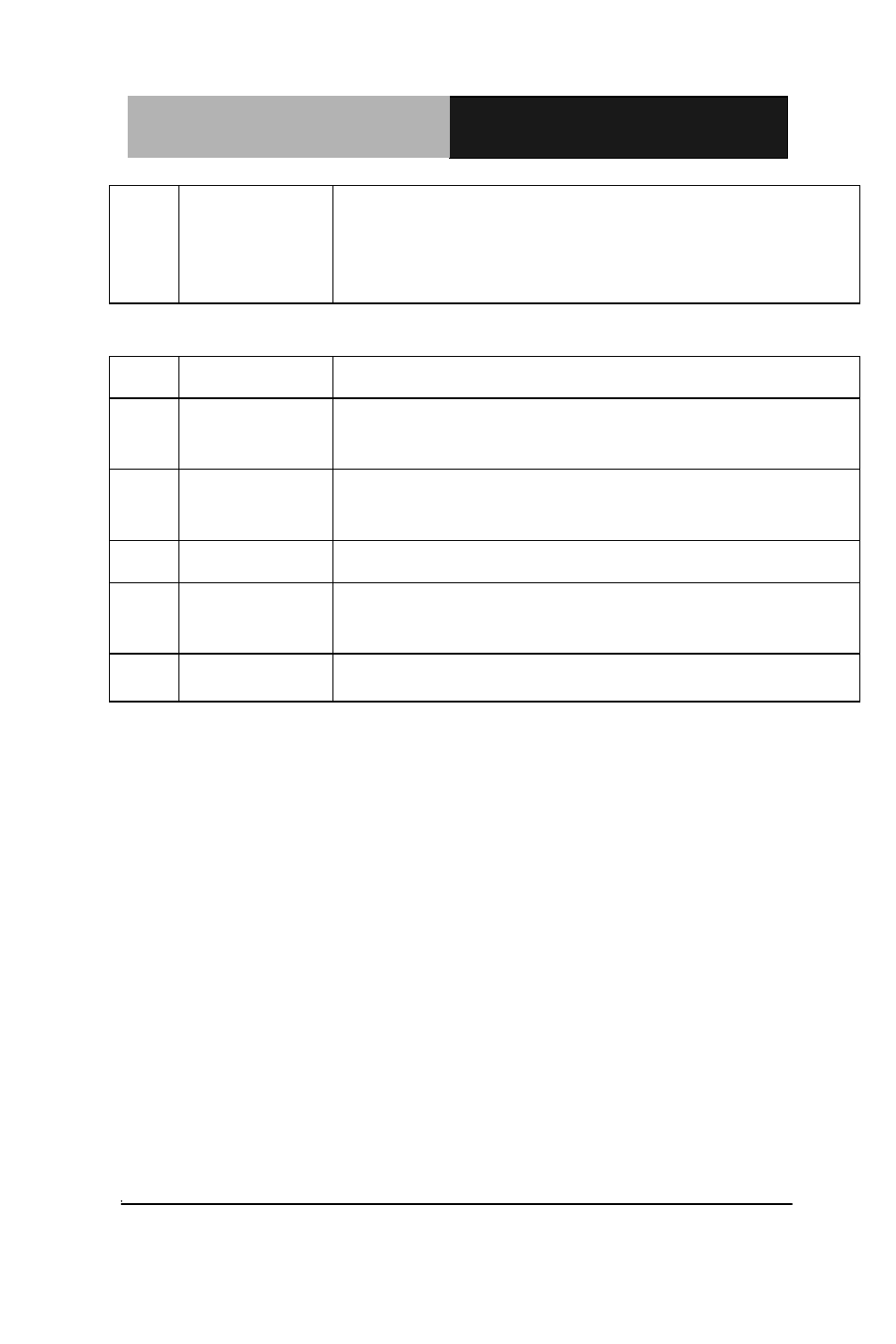

CR F7h. (WDTO# Control & Status Register; Default 00h)

BIT

READ/WRITE

DESCRIPTION

7

R/W

Mouse interrupt reset watch-dog timer enable

0: Watchdog timer is not affected by mouse interrupt.

1: Watchdog timer is reset by mouse interrupt.

6

R/W

Keyboard interrupt reset watch-dog timer enable

0: Watchdog timer is not affected by keyboard interrupt.

1: Watchdog timer is reset by keyboardd interrupt.

5

Write

“1” Only Trigger WDTO# event. This bit is self-clearing.

4

R/W

Write

“0”Clear

WDTO# status bit

0: Watchdog timer is running.

1: Watchdog timer issue time-out event.

3~0

R/W

These bits select IRQ resource for WDTO#. (02h for

SMI# event.)

- PCM-QM77 (172 pages)

- PCM-LN02 (70 pages)

- PCM-9452 (64 pages)

- PCM-8120 (71 pages)

- PCM-5895 Rev.A (78 pages)

- PCM-5895 Rev.B (72 pages)

- EPIC-QM77 (138 pages)

- EPIC-CV07 (128 pages)

- EPIC-HD07 (97 pages)

- EPIC-CV01 Series (44 pages)

- EPIC-9456 (59 pages)

- EPIC-9457 Rev.A (62 pages)

- EPIC-9457 Rev.B (58 pages)

- EPIC-5536 (69 pages)

- EPIC-QM57 (79 pages)

- PCM-3116 (1 page)

- PCMCIA_CompactFlash (28 pages)

- PFM-T096P (41 pages)

- PFM-CVS Rev.B (123 pages)

- PCM-3794 Rev.B (1 page)

- PFM-C42C (25 pages)

- PCM-3660 Rev.B (14 pages)

- PFM-C20N (44 pages)

- PFM-P13DW2 (10 pages)

- PFM-535S (53 pages)

- PFM-540I Rev.B (54 pages)

- PFM-540I Rev.А (62 pages)

- PFM-541I (54 pages)

- PFM-HDS (105 pages)

- PFM-CVS Rev.A (107 pages)

- PFM-LNP (44 pages)

- GENE-QM87 (134 pages)

- GENE-5315 (74 pages)

- GENE-HD05 (116 pages)

- GENE-U15B (60 pages)

- GENE-TC05 (109 pages)

- GENE-LN05 Rev.B (64 pages)

- GENE-9455 Rev.B (63 pages)

- GENE-9455 Rev.А (64 pages)

- GENE-9310 (61 pages)

- GENE-QM67 (89 pages)

- GENE-QM57 (75 pages)

- GENE-QM77 Rev.B (157 pages)

- GENE-QM77 Rev.А (101 pages)

- ETX-701 (62 pages)