AAEON EMB-CV2 User Manual

Page 65

M i n i - I T X

E M B - C V 2

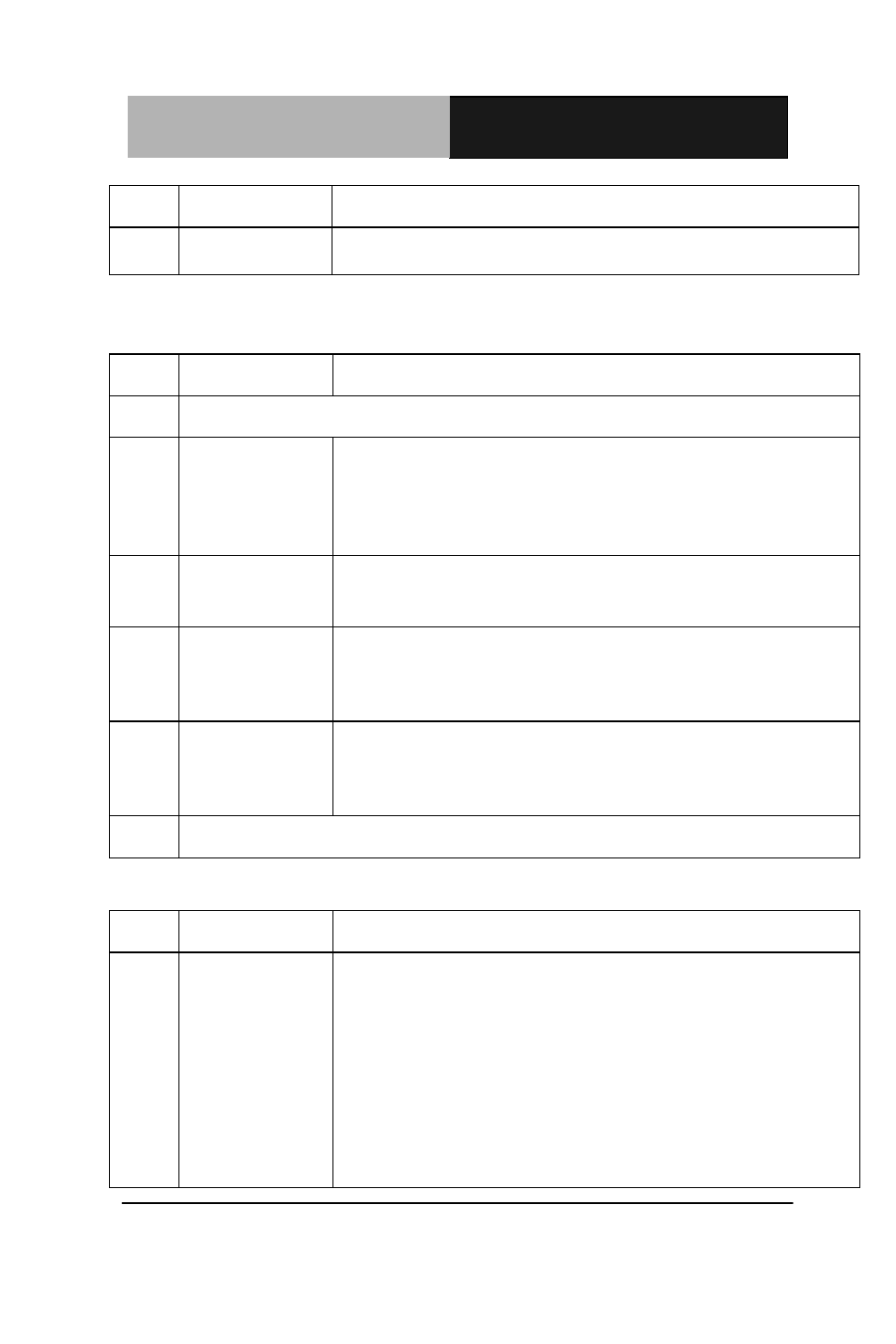

Appendix A Programming the Watchdog Timer

A-4

1

R/W

0: GPIO5 is inactive. 1: GPIO5 is active.

0

R/W

0: WDTO# and PLED are inactive.

1: WDTO# and PLED are inactive.

CR F5h. (WDTO# and KBC P20 Control Mode Register; Default

00h)

BIT

READ/WRITE

DESCRIPTION

7~5

Reserved.

4

R/W

1000 time faster in WDTO# count mode.

0: Disable.

1: Enable.

(If bit-3 is Second Mode, the count mode is 1/1000 Sec.)

(If bit-3 is Minute Mode, the count mode is 1/1000 Min.)

3

R/W

Select WDTO# count mode.

0: Second Mode.

1: Minute Mode.

2

R/W

Enable the rising edge of KBC reset (P20) to issue

time-out event.

0: Disable.

1: Enable.

1

R/W

Disable/ Enable the WDTO# output low pulse to the

KBRST# pin (PIN60)

0: Disable.

1: Enable.

0

Reserved.

CR F6h. (WDTO# Counter Register; Default 00h)

BIT

READ/WRITE

DESCRIPTION

7~0

R/W

Watch Dog Timer Time-out value. Writing a non-zero

value to this register causes the counter to load the

value to Watch Dog Counter and start counting down.

If bits 7 and 6 of CR F7h are set, any Mouse Interrupt or

Keyboard Interrupt event will also cause the reload of

previously-loaded non-zero value to Watch Dog Counter

and start counting down. Reading this resigter returns

current value in Watch Dog Counter instead of Watch

Dog Timer Time-out value.

00h: Time-out Disable