Southbridge configuration, Dram timing configuration – Asus KGNH-D16 User Manual

Page 78

4-20

Chapter 4: BIOS setup

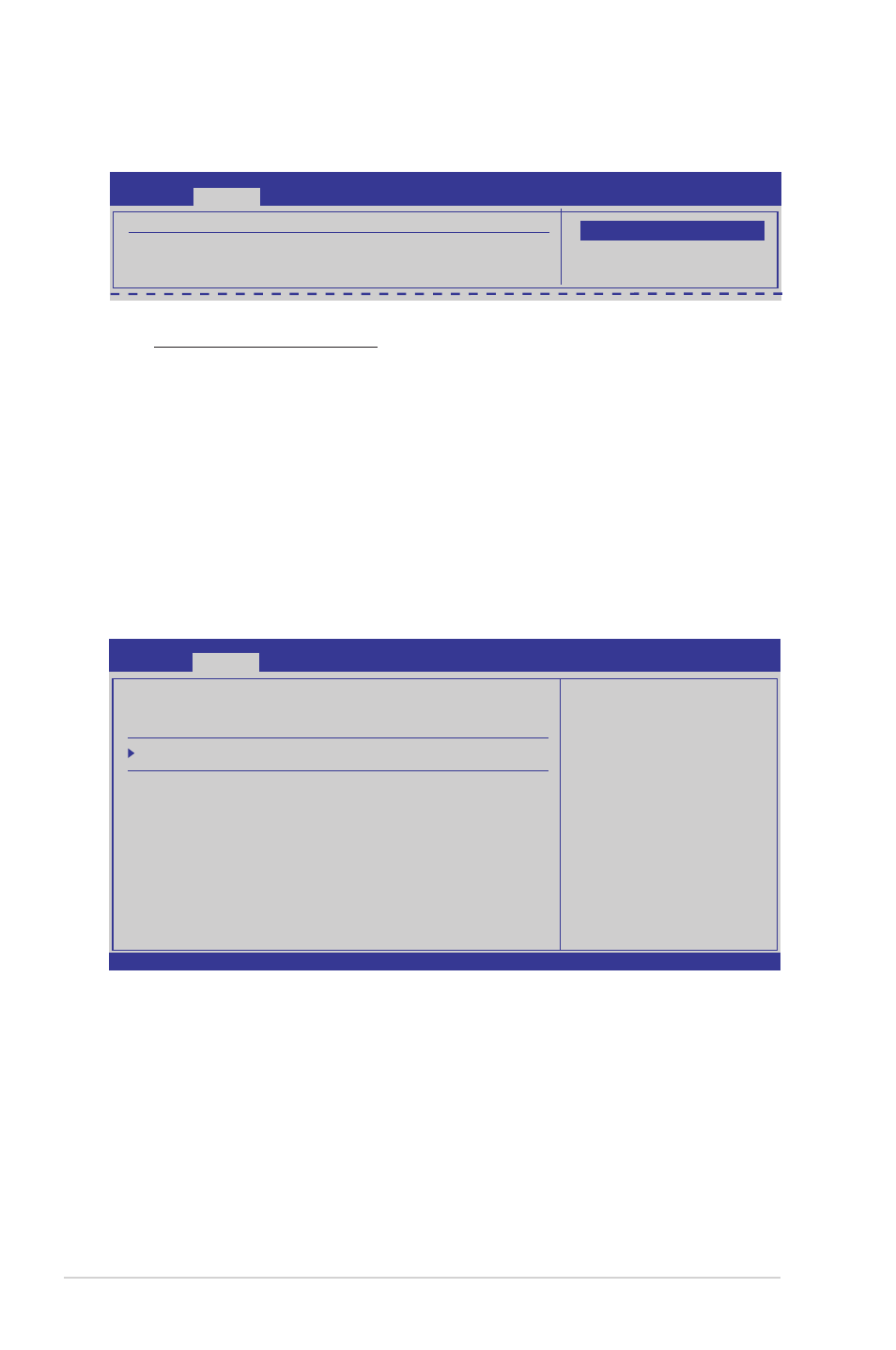

SouthBridge Configuration

v02.61 (C)Copyright 1985-2010, American Megatrends, Inc.

BIOS SETUP UTILITY

Advanced

SouthBridge Chipset Configuration

SP5100 CIMx Version : 5.5.0

SB Debug Configuration

OHCI HC (Bus 0 Dev 18 Fn 0) [Enabled]

OHCI HC (Bus 0 Dev 18 Fn 1) [Enabled]

EHCI HC (Bus 0 Dev 18 Fn 2) [Enabled]

OHCI HC (Bus 0 Dev 19 Fn 0) [Enabled]

OHCI HC (Bus 0 Dev 19 Fn 1) [Enabled]

EHCI HC (Bus 0 Dev 19 Fn 2) [Enabled]

OHCI HC (Bus 0 Dev 18 Fn 5) [Enabled]

←→

Select Screen

↑↓

Select Item

+- Change Option

F1 General Help

F10 Save and Exit

ESC Exit

Options for SB

Debug Features

DRAM Timing Configuration

DRAM Timing Config [Auto]

Configuration options: [Auto] [Manual]

Memory Clock Speed [400 MHz]

Allows you to set the memory clock frequency. This item available only when you set

DRAM Timing Config to [Manual].

Configuration options: [400 MHz] [533 MHz] [667 MHz]

Memory Timing Parameters [CPU Node 0]

Allows you to select which node's timing parameters to display.

BIOS SETUP UTILITY

Advanced

BIOS SETUP UTILITY

Advanced

DRAM Timing Configuration

DRAM Timing Config

[Auto]

Options

Auto

Manual