Pin description – Rainbow Electronics MAX8724 User Manual

Page 11

MAX1908/MAX8724

Low-Cost Multichemistry Battery Chargers

______________________________________________________________________________________

11

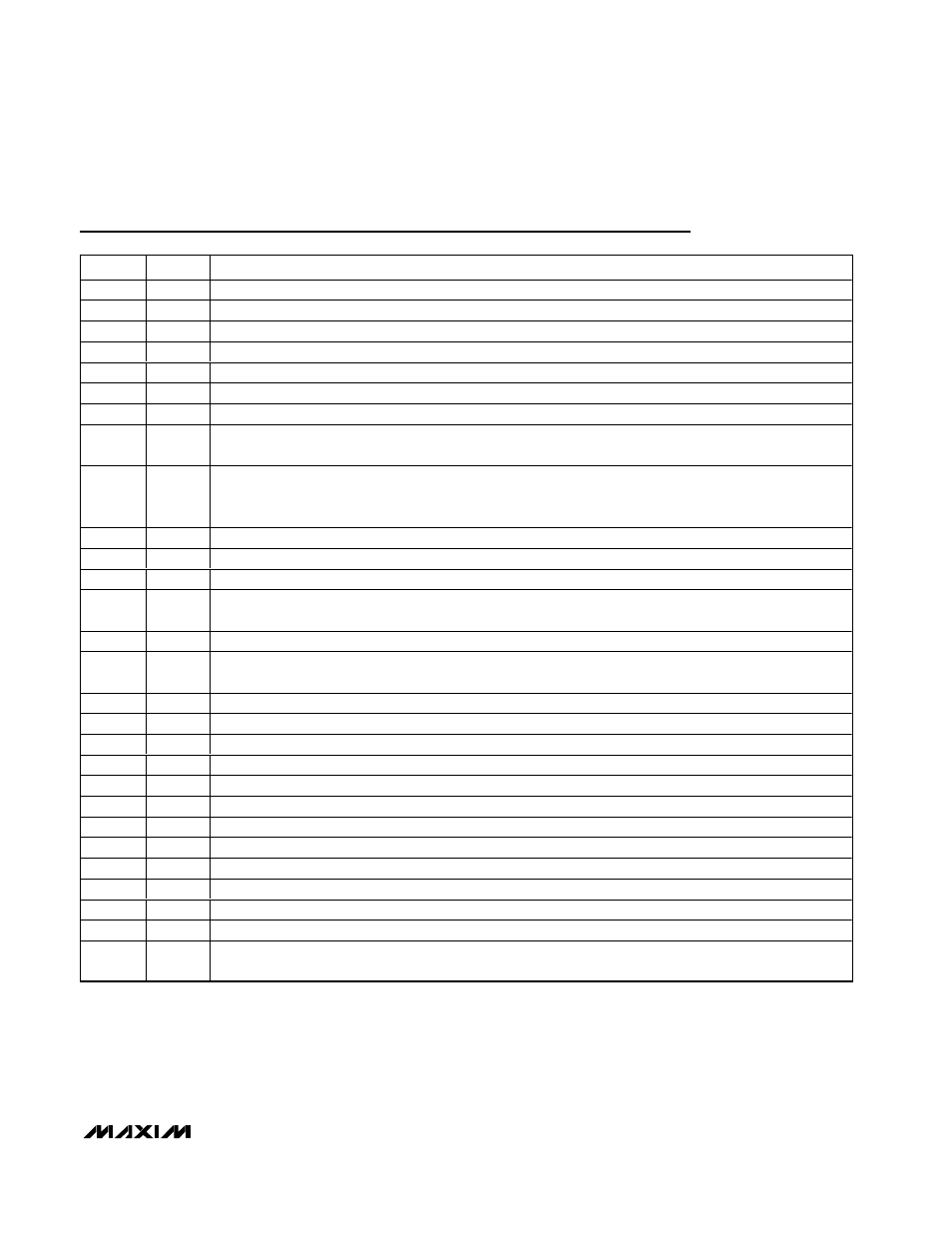

Pin Description

PIN

NAME

FUNCTION

1

DCIN

Charging Voltage Input. Bypass DCIN with a 1µF capacitor to PGND.

2

LDO

D evi ce P ow er S up p l y. Outp ut of the 5.4V l i near r eg ul ator sup p l i ed fr om D C IN . Byp ass w i th a 1µF cap aci tor to GN D .

3

CLS

Source Current-Limit Input. Voltage input for setting the current limit of the input source.

4

REF

4.096V Voltage Reference. Bypass REF with a 1µF capacitor to GND.

5

CCS

Input-Current Regulation Loop-Compensation Point. Connect a 0.01µF capacitor to GND.

6

CCI

Output-Current Regulation Loop-Compensation Point. Connect a 0.01µF capacitor to GND.

7

CCV

Voltage Regulation Loop-Compensation Point. Connect 1k

Ω

in series with 0.1µF capacitor to GND.

8

SHDN

Shutdown Control Input. Drive SHDN logic low to shut down the MAX1908/MAX8724. Use with a thermistor to

detect a hot battery and suspend charging.

9

ICHG

Charge-Current Monitor Output. ICHG is a scaled-down replica of the charger output current. Use ICHG to

monitor the charging current and detect when the chip changes from constant-current mode to constant-

voltage mode. The transconductance of (CSIP - CSIN) to ICHG is 3µA/mV.

10

ACIN

AC Detect Input. Input to an uncommitted comparator. ACIN can be used to detect AC-adapter presence.

11

ACOK

AC Detect Output. High-voltage open-drain output is high impedance when V

ACIN

is less than V

REF

/ 2.

12

REFIN

Reference Input. Allows the ICTL and VCTL inputs to have ratiometric ranges for increased accuracy.

13

ICTL

Output Current-Limit Set Input. ICTL input voltage range is V

REFIN

/ 32 to V

REFIN

. The device shuts down if

ICTL is forced below V

REFIN

/ 100. When ICTL is equal to LDO, the set point for CSIP - CSIN is 45mV.

14

GND

Analog Ground

15

VCTL

Output-Voltage Limit Set Input. VCTL input voltage range is 0 to V

REFIN

. When VCTL is equal to LDO, the set

point is (4.2 x CELLS) V.

16

BATT

Battery Voltage Input

17

CELLS

Cell Count Input. Trilevel input for setting number of cells. GND = 2 cells, float = 3 cells, REFIN = 4 cells.

18

CSIN

Output Current-Sense Negative Input

19

CSIP

Output Current-Sense Positive Input. Connect a current-sense resistor from CSIP to CSIN.

20

PGND

Power Ground

21

DLO

Low-Side Power MOSFET Driver Output. Connect to low-side NMOS gate.

22

DLOV

Low-Side Driver Supply. Bypass DLOV with a 1µF capacitor to GND.

23

LX

High-Side Power MOSFET Driver Power-Return Connection. Connect to the source of the high-side NMOS.

24

BST

High-Side Power MOSFET Driver Power-Supply Connection. Connect a 0.1µF capacitor from LX to BST.

25

DHI

High-Side Power MOSFET Driver Output. Connect to high-side NMOS gate.

26

CSSN

Input Current-Sense Negative Input

27

CSSP

Input Current-Sense Positive Input. Connect a current-sense resistor from CSSP to CSSN.

28

IINP

Input-Current Monitor Output. IINP is a scaled-down replica of the input current. IINP monitors the total

system current. The transconductance of (CSSP - CSSN) to IINP is 3µA/mV.