Multirange inputs, serial 16-bit adcs, Electrical characteristics (continued) – Rainbow Electronics MAX1303 User Manual

Page 5

MAX1302/MAX1303

8-/4-Channel, ±V

REF

Multirange Inputs,

Serial 16-Bit ADCs

_______________________________________________________________________________________

5

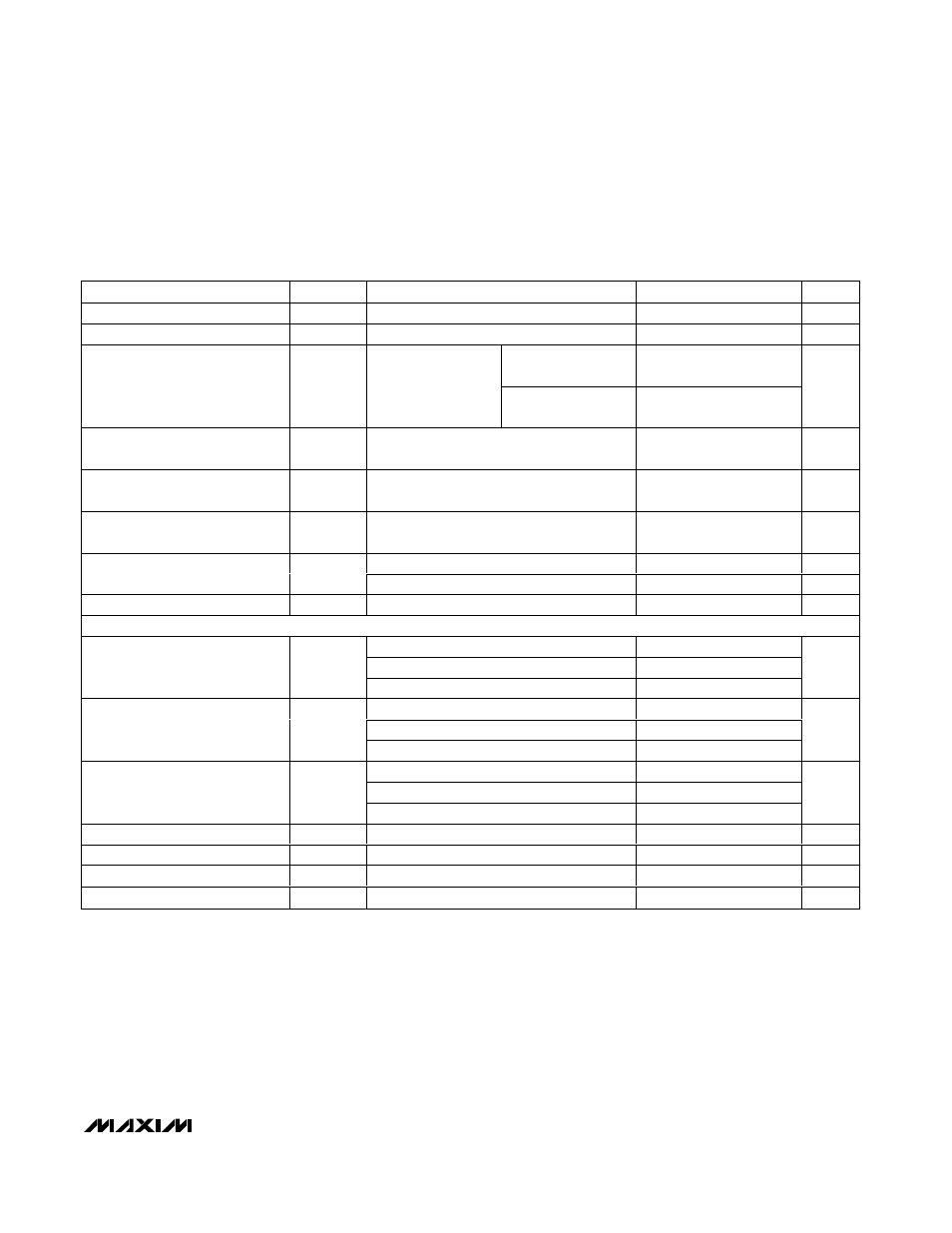

ELECTRICAL CHARACTERISTICS (continued)

(AV

DD1

= AV

DD2

= DV

DD

= DV

DDO

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

CLK

= 3.5MHz (50% duty cycle),

external clock mode, V

REF

= 4.096V (external reference operation), REFCAP = AV

DD1

, maximum single-ended bipolar input range

(±V

REF

), C

DOUT

= 50pF, C

SSTRB

= 50pF, T

A

= -40°C to +85°C, unless otherwise noted. Typical values are at T

A

= +25°C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Preamplifier Supply Voltage

AV

DD2

4.75

5.25

V

Digital I/O Supply Voltage

DV

DDO

2.70

5.25

V

Internal reference

3

3.5

AV

DD1

Supply Current

I

AVDD1

External clock mode,

external acquisition

mode, or internal

clock mode

External reference

2.5

3

mA

DV

DD

Supply Current

I

DVDD

External clock mode, external acquisition

mode, or internal clock mode

0.9

2

mA

AV

DD2

Supply Current

I

AVDD2

External clock mode, external acquisition

mode, or internal clock mode

17.5

25

mA

DV

DDO

Supply Current

I

DVDDO

External clock mode, external acquisition

mode, or internal clock mode

0.2

1

mA

Partial power-down mode

1.3

mA

Total Supply Current

Full power-down mode

2

µA

Power-Supply Rejection Ratio

PSRR

All analog input ranges

±0.5

LSB

TIMING CHARACTERISTICS (Figures 15 and 16)

External clock mode

272

62

External acquisition mode

228

62

SCLK Period

t

CP

Internal clock mode

100

83

µs

External clock mode

109

External acquisition mode

92

SCLK High Pulse Width (Note 6)

t

CH

Internal clock mode

40

ns

External clock mode

109

External acquisition mode

92

SCLK Low Pulse Width (Note 6)

t

CL

Internal clock mode

40

ns

DIN to SCLK Setup

t

DS

40

ns

DIN to SCLK Hold

t

DH

0

ns

SCLK Fall to DOUT Valid

t

DO

40

ns

CS Fall to DOUT Enable

t

DV

40

ns