Wire interface timing specifications, 5v to 5.5v, t – Rainbow Electronics DS2745 User Manual

Page 3

DS2745 Low-Cost I

2

C Battery Monitor

3 of 14

±2

-20°C ≤ T

A

≤ +70°C,

2.5V ≤ V

DD

≤ 5.5V

±3

Input Resistance, VIN

R

IN

15

MW

Input Logic High:

SCL, SDA

V

IH

(Note

1)

1.5

V

Input Logic Low:

SCL, SDA

V

IL

(Note

1)

0.6 V

Output Logic Low:

SDA, PIO

V

OL

I

OL

= 4mA (Note 1)

0.4

V

Pulldown Current: SCL,

SDA

I

PD

0.25

mA

Input Capacitance: SCL,

SDA

C

BUS

50

pF

SLEEP Timeout

t

SLEEP

(Note 3)

2.2 S

Input Logic High:

PIO

V

IH

(Note

1)

V

DD

x 0.7

V

Input Logic Low:

PIO

V

IL

(Note

1)

V

DD

x 0.3

V

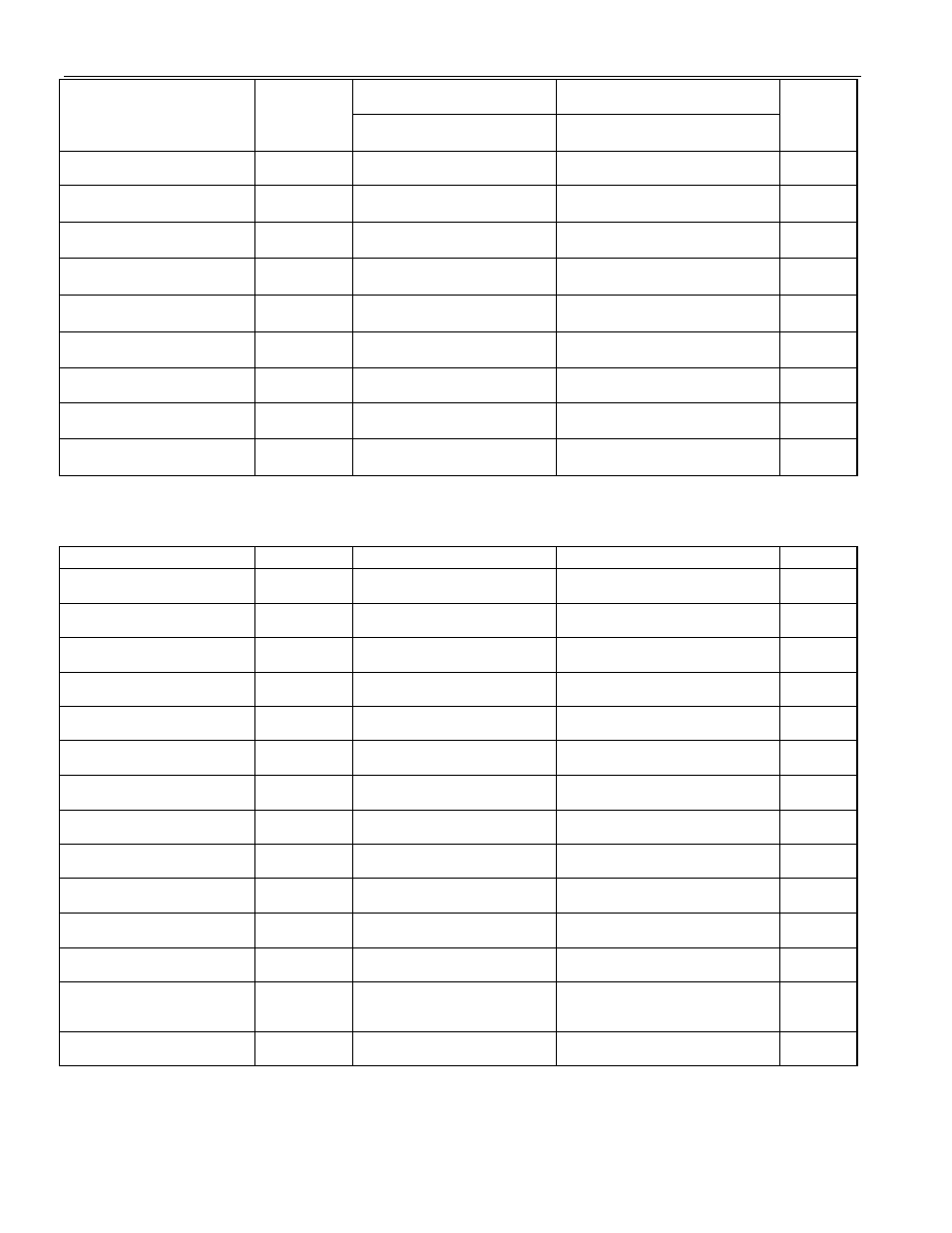

2-WIRE INTERFACE TIMING SPECIFICATIONS

(V

DD

= 2.5V to 5.5V, T

A

= -20

°C to +70°C.)

PARAMETER SYMBOL CONDITIONS MIN TYP

MAX

UNITS

SCL Clock Frequency

fSCL

(Note 6)

0

400

KHz

Bus Free Time Between a

STOP and START Condition

tBUF

1.3

µs

Hold Time (Repeated)

START Condition

tHD:STA

(Note 7)

0.6

µs

Low Period of SCL Clock

tLOW

1.3

µs

High Period of SCL Clock

tHIGH

0.6

µs

Setup Time for a Repeated

START Condition

tSU:STA

0.6

µs

Data Hold Time

tHD:DAT

(Note 8, 9)

0

0.9

µs

Data Setup Time

tSU:DAT

(Note 8)

100

ns

Rise Time of Both SDA and

SCL Signals

tR

20 + 0.1C

B

300 ns

Fall Time of Both SDA and

SCL Signals

tF

20 + 0.1C

B

300 ns

Setup Time for STOP

Condition

tSU:STO

0.6

µs

Spike Pulse Widths

Suppressed by Input Filter

tSP

(Note 10)

0

50

ns

Capacitive Load for Each

Bus

Line

CB

(Note 11)

400

pF

SCL, SDA Input

Capacitance

C

BIN

60

pF