Pin description, Port 2, Port 3 – Rainbow Electronics AT89S53 User Manual

Page 4: Ale/prog, Psen, At89s53

AT89S53

4

Some Port 1 pins provide additional functions. P1.0 and

P1.1 can be configured to be the timer/counter 2 external

count input (P1.0/T2) and the timer/counter 2 trigger input

(P1.1/T2EX), respectively.

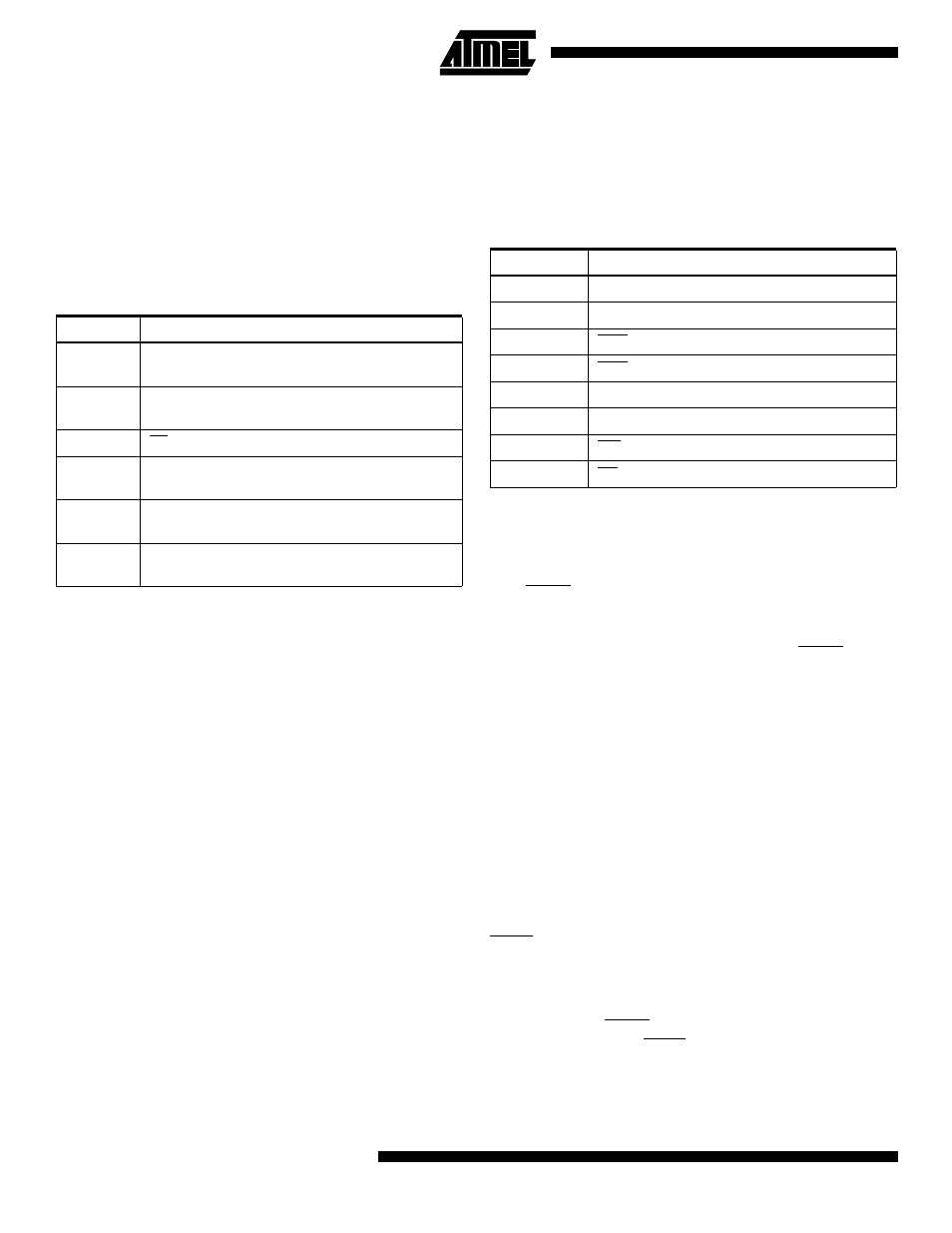

Pin Description

Furthermore, P1.4, P1.5, P1.6, and P1.7 can be configured

as the SPI slave port select, data input/output and shift

clock input/output pins as shown in the following table.

Port 1 also receives the low-order address bytes during

Flash programming and verification.

Port 2

Port 2 is an 8-bit bidirectional I/O port with internal pullups.

The Port 2 output buffers can sink/source four TTL inputs.

When 1s are written to Port 2 pins, they are pulled high by

the internal pullups and can be used as inputs. As inputs,

Port 2 pins that are externally being pulled low will source

current (I

IL

) because of the internal pullups.

Port 2 emits the high-order address byte during fetches

from external program memory and during accesses to

external data memory that use 16-bit addresses (MOVX @

DPTR). In this application, Port 2 uses strong internal pul-

lups when emitting 1s. During accesses to external data

memory that use 8-bit addresses (MOVX @ RI), Port 2

emits the contents of the P2 Special Function Register.

Port 2 also receives the high-order address bits and some

control signals during Flash programming and verification.

Port 3

Port 3 is an 8 bit bidirectional I/O port with internal pullups.

The Port 3 output buffers can sink/source four TTL inputs.

When 1s are written to Port 3 pins, they are pulled high by

the internal pullups and can be used as inputs. As inputs,

Port 3 pins that are externally being pulled low will source

current (I

IL

) because of the pullups.

Port 3 also serves the functions of various special features

of the AT89S53, as shown in the following table.

Port 3 also receives some control signals for Flash pro-

gramming and verification.

RST

Reset input. A high on this pin for two machine cycles while

the oscillator is running resets the device.

ALE/PROG

Address Latch Enable is an output pulse for latching the

low byte of the address during accesses to external mem-

ory. This pin is also the program pulse input (PROG) during

Flash programming.

In normal operation, ALE is emitted at a constant rate of 1/6

the oscillator frequency and may be used for external tim-

ing or clocking purposes. Note, however, that one ALE

pulse is skipped during each access to external data

memory.

If desired, ALE operation can be disabled by setting bit 0 of

SFR location 8EH. With the bit set, ALE is active only dur-

ing a MOVX or MOVC instruction. Otherwise, the pin is

weakly pulled high. Setting the ALE-disable bit has no

effect if the microcontroller is in external execution mode.

PSEN

Program Store Enable is the read strobe to external pro-

gram memory.

When the AT89S53 is executing code from external pro-

gram memory, PSEN is activated twice each machine

cycle, except that two PSEN activations are skipped during

each access to external data memory.

Port Pin

Alternate Functions

P1.0

T2 (external count input to Timer/Counter 2),

clock-out

P1.1

T2EX (Timer/Counter 2 capture/reload trigger

and direction control)

P1.4

SS (Slave port select input)

P1.5

MOSI (Master data output, slave data input pin

for SPI channel)

P1.6

MISO (Master data input, slave data output pin

for SPI channel)

P1.7

SCK (Master clock output, slave clock input pin

for SPI channel)

Port Pin

Alternate Functions

P3.0

RXD (serial input port)

P3.1

TXD (serial output port)

P3.2

INT0 (external interrupt 0)

P3.3

INT1 (external interrupt 1)

P3.4

T0 (timer 0 external input)

P3.5

T1 (timer 1 external input)

P3.6

WR (external data memory write strobe)

P3.7

RD (external data memory read strobe)