Restrictions on certain instructions, Branching instructions, Movx-related instructions, data memory – Rainbow Electronics AT89C4051 User Manual

Page 6: Program memory lock bits, Lock bit protection modes(1)

6

AT89C4051

1001D–06/01

Restrictions on

Certain Instructions

The AT89C4051 is an economical and cost-effective member of Atmel’s growing family

of microcontrollers. It contains 4K bytes of Flash program memory. It is fully compatible

with the MCS-51 architecture, and can be programmed using the MCS-51 instruction

set. However, there are a few considerations one must keep in mind when utilizing cer-

tain instructions to program this device.

All the instructions related to jumping or branching should be restricted such that the

destination address falls within the physical program memory space of the device, which

is 4K for the AT89C4051. This should be the responsibility of the software programmer.

For example, LJMP 0FE0H would be a valid instruction for the AT89C4051 (with 4K of

memory), whereas LJMP 1000H would not.

Branching Instructions

LCALL, LJMP, ACALL, AJMP, SJMP, JMP @A+DPTR. These unconditional branching

instructions will execute correctly as long as the programmer keeps in mind that the des-

tination branching address must fall within the physical boundaries of the program

memory size (locations 00H to FFFH for the 89C4051). Violating the physical space lim-

its may cause unknown program behavior.

CJNE [...], DJNZ [...], JB, JNB, JC, JNC, JBC, JZ, JNZ With these conditional branching

instructions the same rule above applies. Again, violating the memory boundaries may

cause erratic execution.

For applications involving interrupts, the normal interrupt service routine address loca-

tions of the 80C51 family architecture have been preserved.

MOVX-related

Instructions, Data

Memory

The AT89C4051 contains 128 bytes of internal data memory. Thus, in the AT89C4051

the stack depth is limited to 128 bytes, the amount of available RAM. External DATA

memory access is not supported in this device, nor is external PROGRAM memory exe-

cution. Therefore, no MOVX [...] instructions should be included in the program.

A typical 80C51 assembler will still assemble instructions, even if they are written in vio-

lation of the restrictions mentioned above. It is the responsibility of the controller user to

know the physical features and limitations of the device being used and adjust the

instructions used correspondingly.

Program Memory

Lock Bits

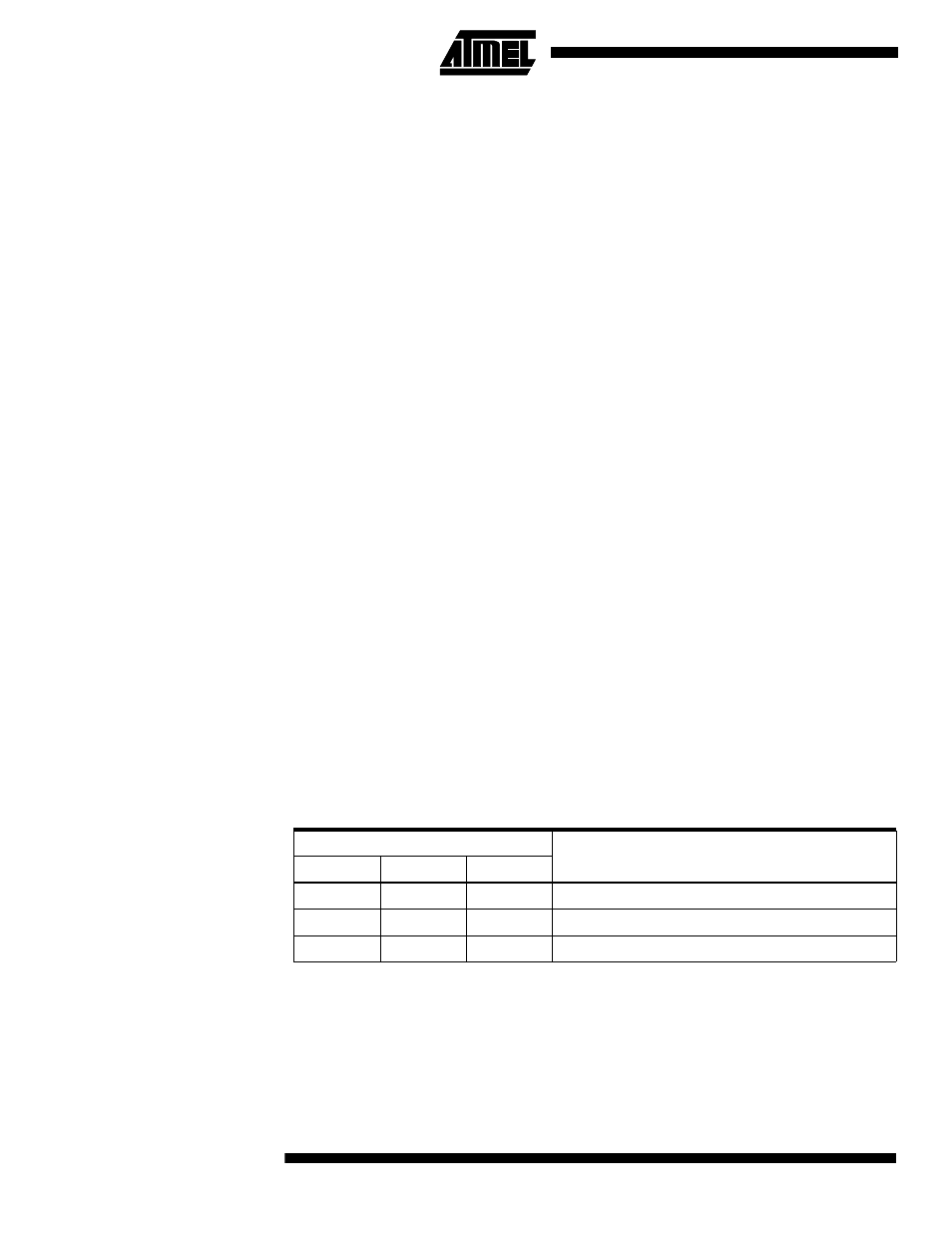

On the chip are two lock bits which can be left unprogrammed (U) or can be pro-

grammed (P) to obtain the additional features listed in the following table:

Note:

1. The Lock Bits can only be erased with the Chip Erase operation.

Lock Bit Protection Modes

Program Lock Bits

Protection Type

LB1

LB2

1

U

U

No program lock features

2

P

U

Further programming of the Flash is disabled

3

P

P

Same as mode 2, also verify is disabled