Table 1. irs pin functions, 8 output pins, 9 application schematics – Rainbow Electronics ADC10080 User Manual

Page 17: Applications information

Applications Information

(Continued)

TABLE 1. IRS Pin Functions

IRS Pin

Full-Scale Input

V

DDA

2.0V

P-P

V

SSA

1.5V

P-P

Floating

1.0V

P-P

1.8 OUTPUT PINS

The ADC10080 has 10 TTL/CMOS compatible Data Output

pins. The offset binary data is present at these outputs while

the DF and STBY pins are low. While the t

OD

time provides

information about output timing, a simple way to capture a

valid output is to latch the data on the rising edge of the

conversion clock. Be very careful when driving a high ca-

pacitance bus. The more capacitance the output drivers

must charge for each conversion, the more instantaneous

digital current flows through V

DDIO

and V

SSIO

. These large

charging current spikes can cause on-chip ground noise and

couple into the analog circuitry, degrading dynamic perfor-

mance. Adequate bypassing, limiting output capacitance and

careful attention to the ground plane will reduce this prob-

lem. Additionally, bus capacitance beyond the specified

10 pF/pin will cause t

OD

to increase, making it difficult to

properly latch the ADC output data. The result could be an

apparent reduction in dynamic performance. To minimize

noise due to output switching, minimize the load currents at

the digital outputs. This can be done by connecting buffers

between the ADC outputs and any other circuitry. Only one

driven input should be ADC pins, will isolate the outputs from

trace and other circuit capacitances and limit the output

currents, which could otherwise result in performance deg-

radation.

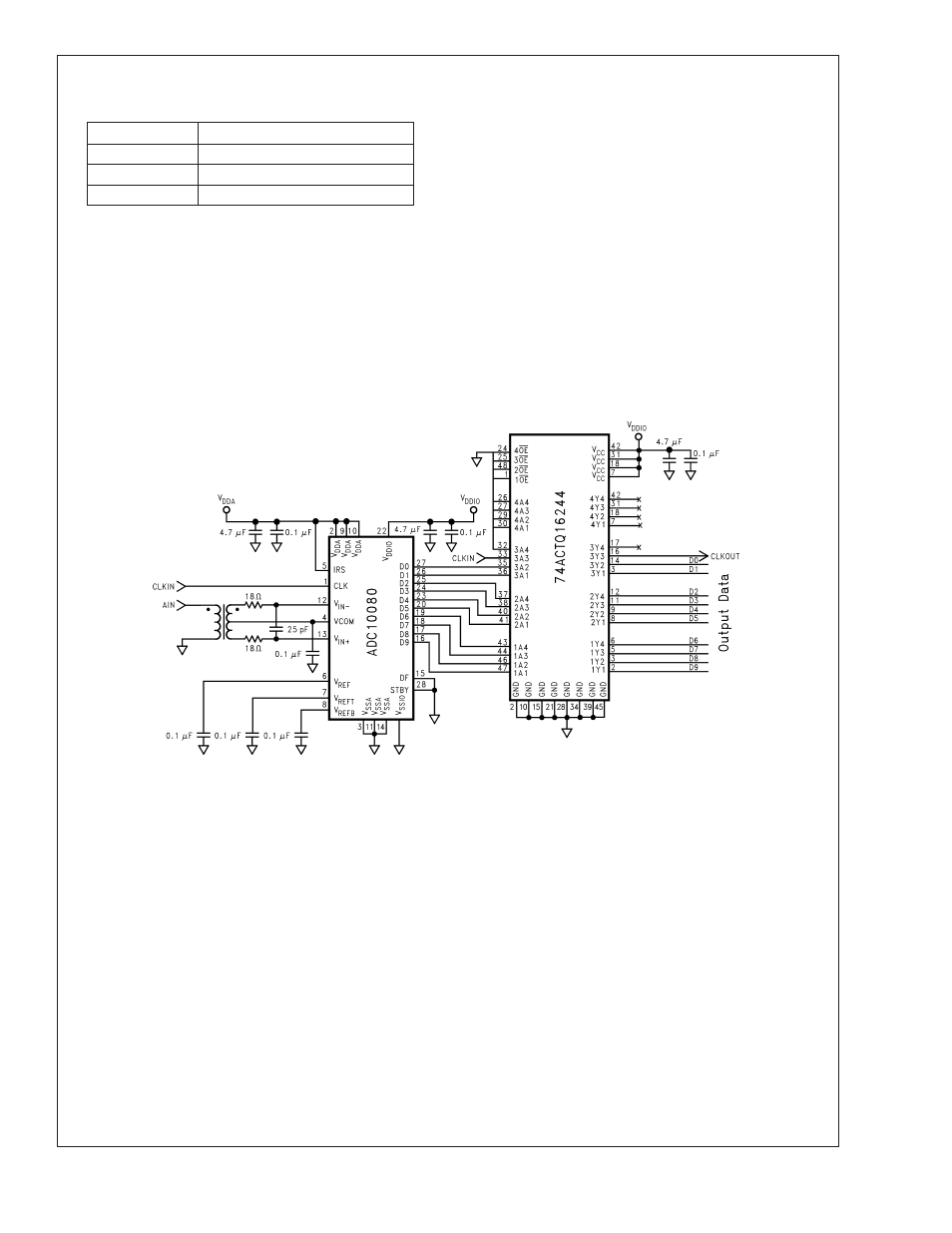

1.9 APPLICATION SCHEMATICS

The following figures show simple examples of using the

ADC10080. Figure 5 shows a typical differentially driven

input. Figure 6 shows a single ended application circuit.

20048549

FIGURE 5. A Simple Application Using a Differential Driving Source

ADC10080

www.national.com

17