At89s51 – Rainbow Electronics АТ89С51 User Manual

Page 7

7

AT89S51

2487A–10/01

User software should not write 1s to these unlisted locations, since they may be used in future

products to invoke new features. In that case, the reset or inactive values of the new bits will

always be 0.

Interrupt Registers: The individual interrupt enable bits are in the IE register. Two priorities

can be set for each of the five interrupt sources in the IP register.

Dual Data Pointer Registers: To facilitate accessing both internal and external data memory,

two banks of 16-bit Data Pointer Registers are provided: DP0 at SFR address locations 82H-

83H and DP1 at 84H-85H. Bit DPS = 0 in SFR AUXR1 selects DP0 and DPS = 1 selects DP1.

The user should always initialize the DPS bit to the appropriate value before accessing the

respective Data Pointer Register.

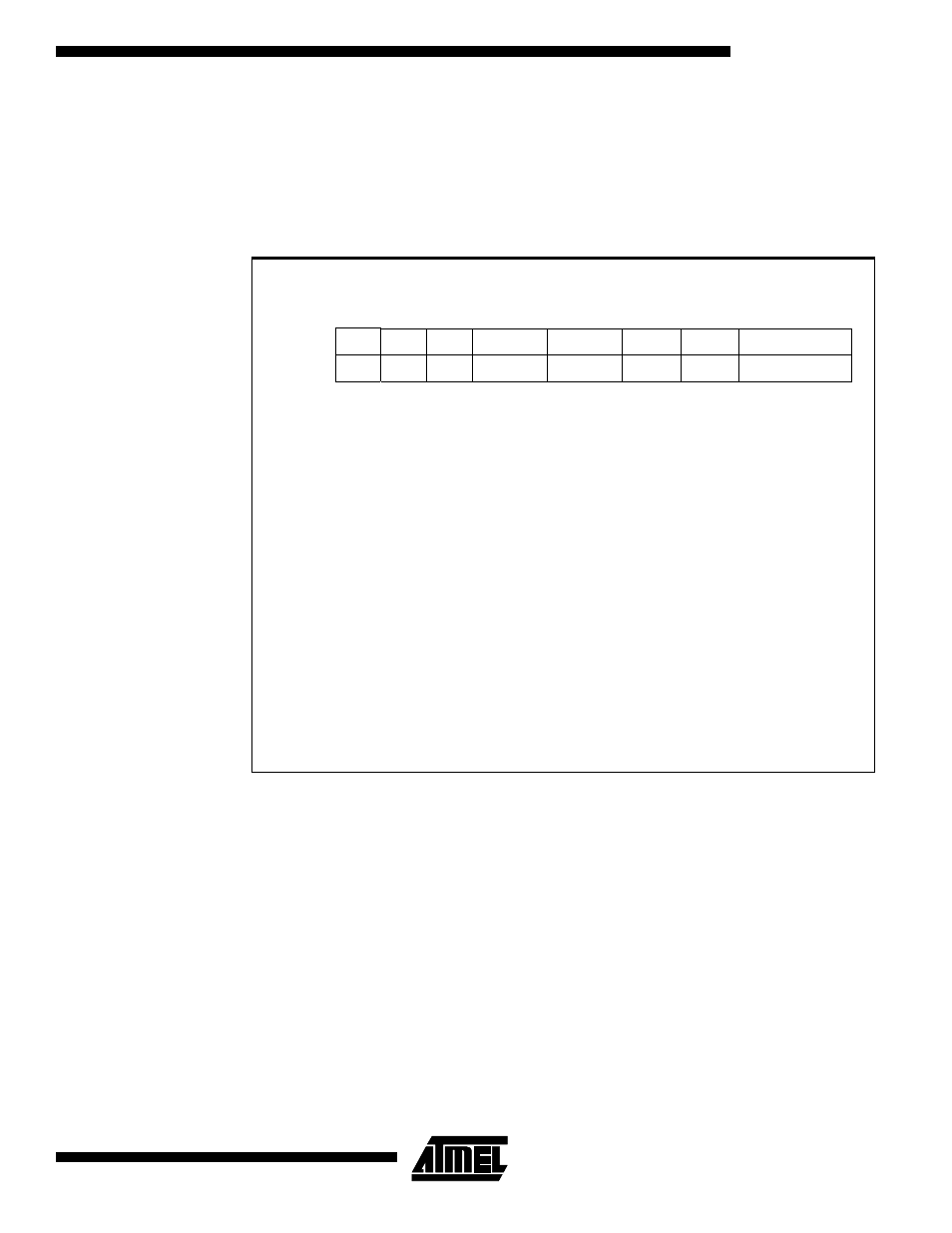

Table 2. AUXR: Auxiliary Register

AUXR

Address = 8EH

Reset Value = XXX00XX0B

Not Bit

Addressable

–

–

–

WDIDLE

DISRTO

–

–

DISALE

Bit

7

6

5

4

3

2

1

0

–

Reserved for future expansion

DISALE

Disable/Enable ALE

DISALE

Operating Mode

0

ALE is emitted at a constant rate of 1/6 the oscillator frequency

1

ALE is active only during a MOVX or MOVC instruction

DISRTO

Disable/Enable Reset out

DISRTO

0

Reset pin is driven High after WDT times out

1

Reset pin is input only

WDIDLE

Disable/Enable WDT in IDLE mode

WDIDLE

0

WDT continues to count in IDLE mode

1

WDT halts counting in IDLE mode