Electrical characteristics (continued) – Rainbow Electronics MAX19516 User Manual

Page 6

MAX19516

Dual-Channel, 10-Bit, 100Msps ADC

6

_______________________________________________________________________________________

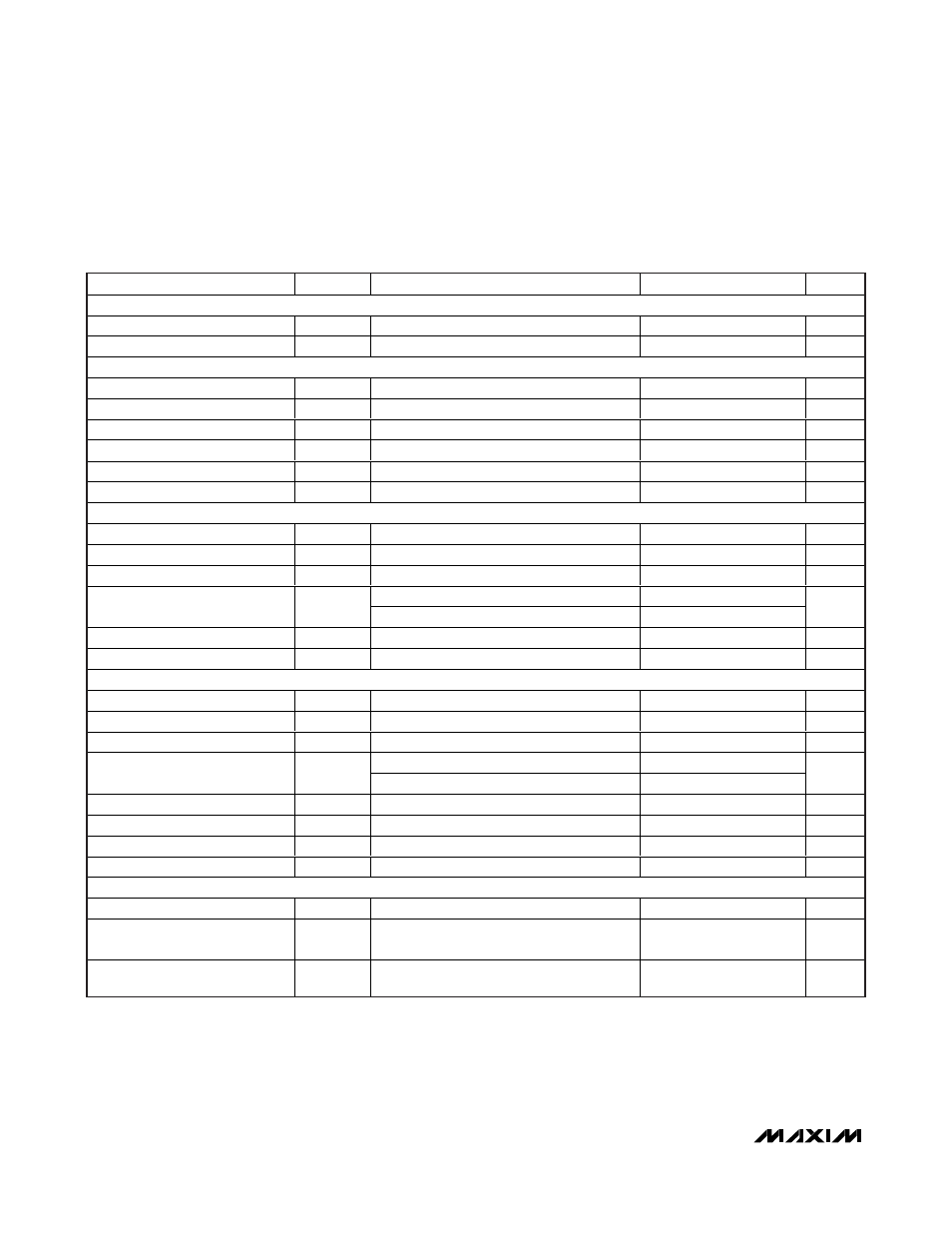

ELECTRICAL CHARACTERISTICS (continued)

(V

AVDD

= V

OVDD

= 1.8V, internal reference, differential clock, V

CLK

= 1.5V

P-P

, f

CLK

= 100MHz, A

IN

= -0.5dBFS, data output termina-

tion = 50

Ω, T

A

= -40°C to +85°C, unless otherwise noted. Typical values are at T

A

= +25°C.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

POWER-MANAGEMENT CHARACTERISTICS

Wake-Up Time from Shutdown

t

WAKE

Internal reference, C

REFIO

= 0.1µF (10

τ)

5

ms

Wake-Up Time from Standby

t

WAKE

Internal reference

15

µs

SERIAL-PORT INTERFACE TIMING (Note 2) (Figure 7)

SCLK Period

t

SCLK

50

ns

SCLK to

CS Setup Time

t

CSS

10

ns

SCLK to

CS Hold Time

t

CSH

10

ns

SDIN to SCLK Setup Time

t

SDS

Serial-data write

10

ns

SDIN to SCLK Hold Time

t

SDH

Serial-data write

0

ns

SCLK to SDIN Output Data Delay

t

SDD

Serial-data read

10

ns

TIMING CHARACTERISTICS—DUAL BUS PARALLEL MODE (Figure 9) (Default Timing, see Table 5)

Clock Pulse-Width High

t

CH

5.0

ns

Clock Pulse-Width Low

t

CL

5.0

ns

Clock Duty Cycle

t

CH

/t

CLK

30 to 70

%

C

L

= 10pF, V

OVDD

= 1.8V (Note 2)

2.9

4.8

6.6

Data Delay After Rising Edge of

CLK+

t

DD

C

L

= 10pF, V

OVDD

= 3.3V

3.6

ns

Data to DCLK Setup Time

t

SETUP

C

L

= 10pF, V

OVDD

= 1.8V (Note 2)

8.2

8.8

ns

Data to DCLK Hold Time

t

HOLD

C

L

= 10pF, V

OVDD

= 1.8V (Note 2)

0.7

1.2

ns

TIMING CHARACTERISTICS—MULTIPLEXED BUS PARALLEL MODE (Figure 10) (Default Timing, see Table 5)

Clock Pulse-Width High

t

CH

5.0

ns

Clock Pulse-Width Low

t

CL

5.0

ns

Clock Duty Cycle

t

CH

/t

CLK

30 to 70

%

C

L

= 10pF, V

OVDD

= 1.8V (Note 2)

2.6

4.4

6.5

Data Delay After Rising Edge of

CLK+

t

DD

C

L

= 10pF, V

OVDD

= 3.3V

3.5

ns

Data to DCLK Setup Time

t

SETUP

C

L

= 10pF, V

OVDD

= 1.8V (Note 2)

2.8

4.0

ns

Data to DCLK Hold Time

t

HOLD

C

L

= 10pF, V

OVDD

= 1.8V (Note 2)

-0.2

1.0

ns

DCLK Duty Cycle

t

DCH

/t

CLK

C

L

= 10pF, V

OVDD

= 1.8V (Note 2)

42

50

59

%

MUX Data Duty Cycle

t

CHA

/t

CLK

C

L

= 10pF, V

OVDD

= 1.8V (Note 2)

40

50

65

%

TIMING CHARACTERISTICS—SYNCHRONIZATION (Figure 12)

Setup Time for Valid Clock Edge

t

SUV

Edge mode (Note 2)

0.7

ns

Hold-Off Time for Invalid Clock

Edge

t

HO

Edge mode (Note 2)

0.5

ns

Minimum Synchronization Pulse

Width

Relative to input clock period

2

Cycles