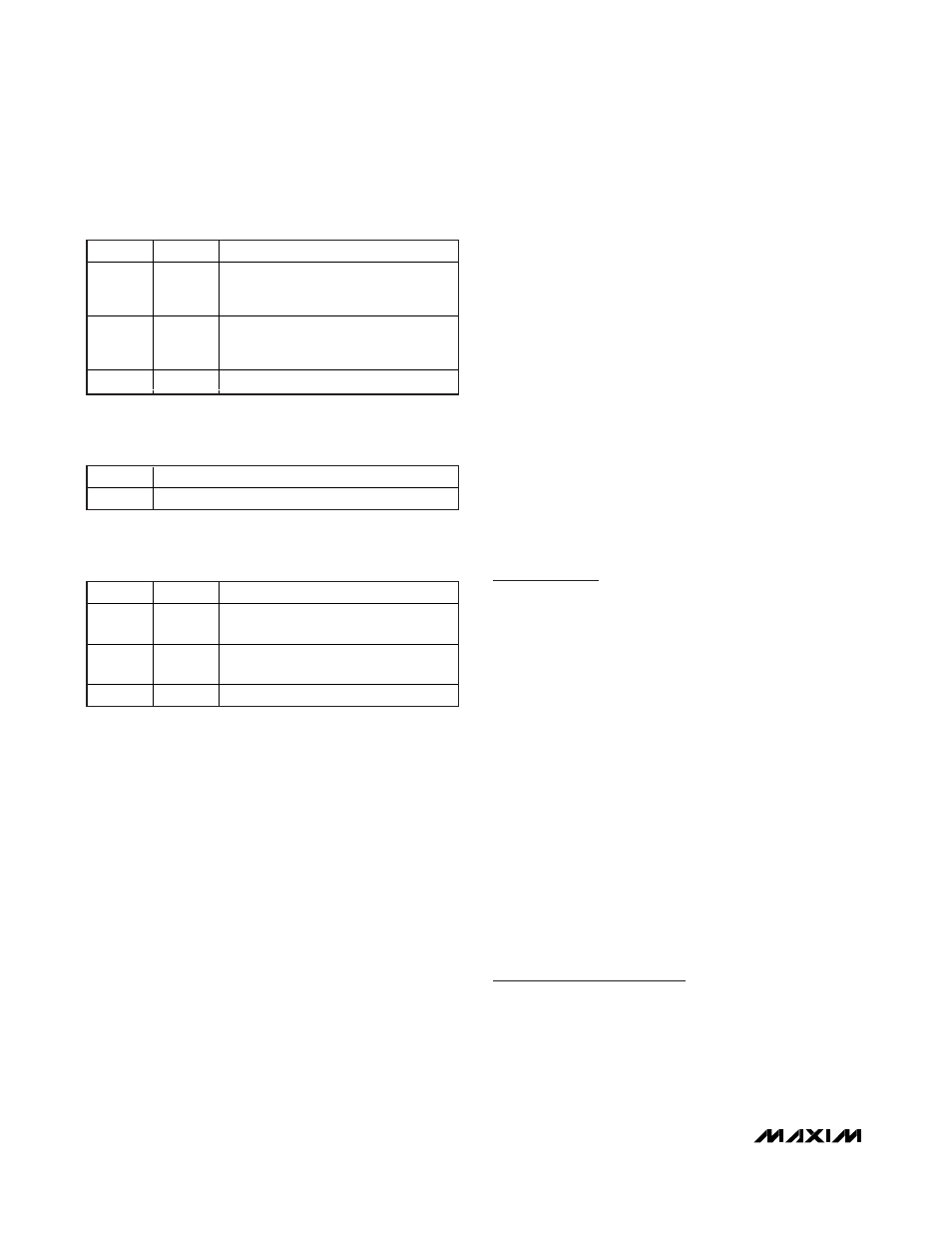

Applications information, Chip information, Table 2. hv truth table – Rainbow Electronics MAX4885E User Manual

Page 8: Table 3. ddc truth table, Table 1. rgb truth table

Horizontal/Vertical Sync Level Shifter

HSYNC/VSYNC are buffered to provide level shifting

and drive capability to meet the VESA specification.

Display-Data Channel Multiplexer

The MAX4885E provides two voltage-clamped switches

to route DDC signals (see Table 3). Each switch clamps

signals to a diode drop less than the voltage applied on

V

L

. Supply +3.3V on V

L

to provide voltage clamping for

VESA I

2

C-compatible signals. If voltage clamping is not

required, connect V

L

to V

CC

. The SDA_ and SCL_

switches are identical, and each switch can be used to

route either SDA_ and SCL_ signals.

ESD Protection

As with all Maxim devices, ESD-protection structures

are incorporated on all pins to protect against electro-

static discharges encountered during handling and

assembly. Additionally, the MAX4885E is protected to

±15kV on RGB, HSYNC, VSYNC, SDA_ and SCL_

outputs by the Human Body Model (HBM). See the

Pin

Description

section. For optimum ESD performance,

bypass each V

CC

pin to ground with a 0.1µF or larger

ceramic capacitor.

Human Body Model (HBM)

Several ESD testing standards exist for measuring the

robustness of ESD structures. The ESD protection of

the MAX4885E is characterized with the Human Body

Model. Figure 3 shows the model used to simulate an

ESD event resulting from contact with the human body.

The model consists of a 100pF storage capacitor that is

charged to a high voltage, then discharged through a

1.5kΩ resistor. Figure 4 shows the current waveform

when the storage capacitor is discharged into a low

impedance.

ESD Test Conditions

ESD performance depends on a variety of conditions.

Please contact Maxim for a reliability report document-

ing test setup, methodology, and results.

Applications Information

The MAX4885E provides the level shifting necessary to

drive two standard VGA ports from a graphics con-

troller as low as +2.2V. Internal buffers drive the

HSYNC and VSYNC signals to VGA standard TTL lev-

els. The DDC multiplexer provides level shifting by

clamping signals to a diode drop less than V

L

(see the

Typical Operating Circuit

). Connect V

L

to +3.3V for nor-

mal operation, or to V

CC

to disable voltage clamping for

DDC signals.

Power-Supply Decoupling

Bypass each V

CC

pin and V

L

to ground with a 0.1µF

or larger ceramic capacitor as close as possible to the

device.

PCB Layout

High-speed switches such as the MAX4885E require

proper PCB layout for optimum performance. Ensure

that impedance-controlled PCB traces for high-speed

signals are matched in length and as short as possible.

Connect the exposed pad to a solid ground plane.

Chip Information

PROCESS: BiCMOS

MAX4885E

Ultra-Low Capacitance 1:2 VGA

Switch with ±15kV ESD

8

_______________________________________________________________________________________

EN

FUNCTION

0

H_, V_ = 0

Table 2. HV Truth Table

X = Don’t care.

EN

SEL

FUNCTION

1

0

SDA0 to SDA1

SCL0 to SCL1

1

1

SDA0 to SDA2

SCL0 to SCL2

0

X

SDA_, SCL_, high impedance

Table 3. DDC Truth Table

X = Don’t care.

EN

SEL

FUNCTION

1

0

R0 to R1

G0 to G1

B0 to B1

1

1

R0 to R2

G0 to G2

B0 to B2

0

X

R_, B_, and G_, high impedance

Table 1. RGB Truth Table

X = Don’t care.