12 uart interface controller, 1 overview, Uart interface controller – Rainbow Electronics NUC120 User Manual

Page 45: Overview, Nuc120 series data sheet

NUC120 Series DATA SHEET

Publication Release Date: May 31, 2010

- 45 -

Revision V1.02

5.12 UART Interface Controller

This MCU provides three channels of Universal Asynchronous Receiver/Transmitters (UART). UART0

supports High Speed UART and UART1~2 perform Normal Speed UARTs, besides, only UART0 and

UART1 support flow control function.

5.12.1 Overview

The Universal Asynchronous Receiver/Transmitter (UART) performs a serial-to-parallel conversion on

data received from the peripheral, and a parallel-to-serial conversion on data transmitted from the

CPU. The UART controller also supports LIN master mode function and IrDA SIR Function. Each

UART channel supports seven types of interrupts including transmitter FIFO empty

interrupt(INT_THRE), receiver threshold level reaching interrupt (INT_RDA), line status interrupt

(overrun error or parity error or framing error or break interrupt) (INT_RLS), time out interrupt

(INT_Tout), MODEM/Wakeup status interrupt (INT_Modem), Buffer error interrupt (INT_Buf_Err) and

LIN receiver break field detected interrupt.

The UART0 are built-in with a 64-byte transmitter FIFO (TX_FIFO) and a 64-byte receiver FIFO

(RX_FIFO) that reduces the number of interrupts presented to the CPU and the UART1~2 are

equipped 16-byte transmitter FIFO (TX_FIFO) and 16-byte receiver FIFO (RX_FIFO). The CPU can

read the status of the UART at any time during the operation. The reported status information includes

the type and condition of the transfer operations being performed by the UART, as well as 4 error

conditions (parity error, overrun error, framing error and break interrupt) probably occur while receiving

data. The UART includes a programmable baud rate generator that is capable of dividing crystal clock

input by divisors to produce the clock that transmitter and receiver need. The baud rate equation is

Baud Rate = UART_CLK / M * [BRD + 2], where M and BRD are defined in Baud Rate Divider

Register (UA_BAUD). Table 5-4 lists the equations in the various conditions.

The UART0 and UART1 controllers support auto-flow control function that uses two low-level signals,

/CTS (clear-to-send) and /RTS (request-to-send), to control the flow of data transfer between the

UART and external devices (ex: Modem). When auto-flow is enabled, the UART is not allowed to

receive data until the UART asserts /RTS to external device. When the number of bytes in the Rx

FIFO equals the value of RTS_Tri_Lev(UA_FCR[19:16]), the /RTS is de-asserted. The UART sends

data out when UART controller detects /CTS is asserted from external device. If a validly asserted

/CTS is not detected the UART controller will not send data out.

The UART controllers also provides Serial IrDA (SIR, Serial Infrared) function (User must set

IrDA_EN(UA_FUN_SEL[1])to enable IrDA function). The SIR specification defines a short-range

infrared asynchronous serial transmission mode with one start bit, 8 data bits, and 1 stop bit. The

maximum data rate is 115.2 Kbps (half duplex). The IrDA SIR block contains an IrDA SIR Protocol

encoder/decoder. The IrDA SIR protocol is half-duplex only. So it cannot transmit and receive data at

the same time. The IrDA SIR physical layer specifies a minimum 10ms transfer delay between

transmission and reception. This delay feature must be implemented by software.

The alternate function of UART controllers is LIN(Local Interconnect Network) function. The LIN mode

is selected by setting the LIN_EN bit in UA_FUN_SEL register. In LIN mode, one start bit and 8-bit

data format with 1-bit stop bit are required in accordance with the LIN standard.

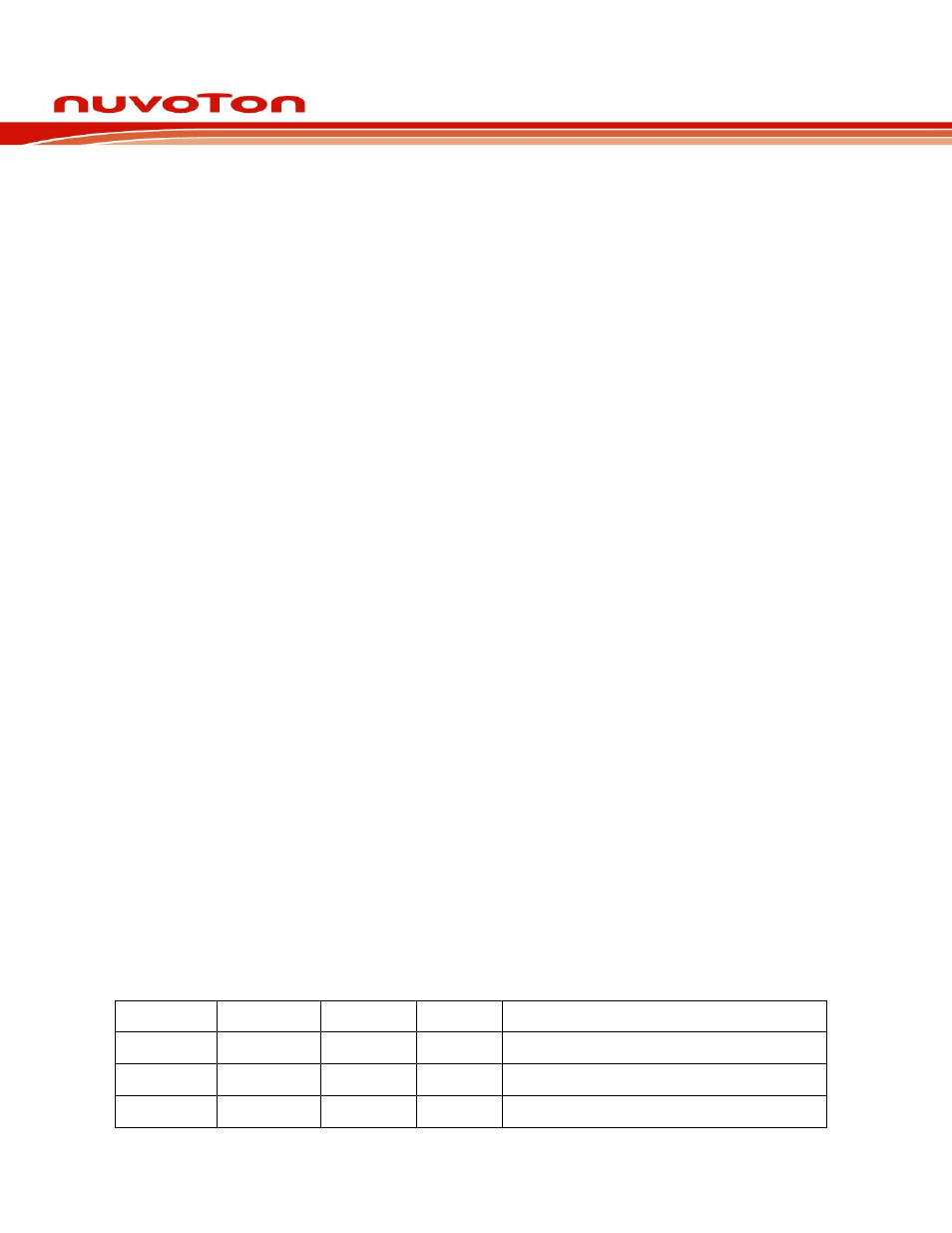

Table 5-4 UART Baud Rate Equation

DIV_X_EN

DIV_X_ONE

Divider X

BRD

Baud rate equation

Disable

0

B

A

UART_CLK / [16 * (A+2)]

Enable

0

B

A

UART_CLK / [(B+1) * (A+2)] , B must >= 8

Enable

1

B

A

UART_CLK / (A+2), A must >=3