Rainbow Electronics W78C801 User Manual

Page 3

W78C801

Publication Release Date: February 1999

- 3 -

Revision A3

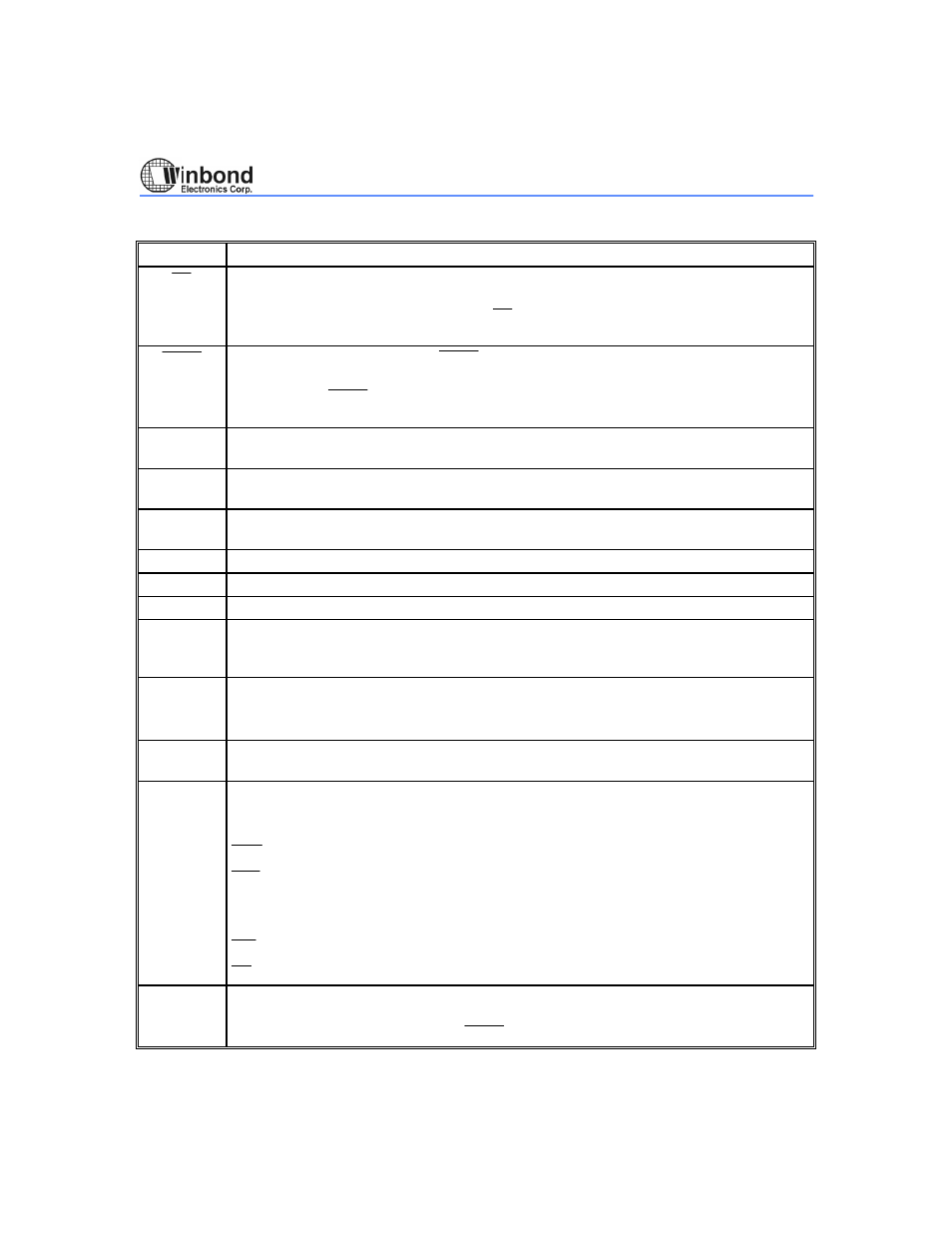

PIN DESCRIPTION

SYMBOL

DESCRIPTIONS

EA

EXTERNAL ACCESS ENABLE: This pin forces the processor to execute out of

external ROM. It should be kept high to access internal ROM. The ROM address and

data will not be presented on the bus if

EA

pin is high and the program counter is

within on-chip ROM area. Otherwise they will be presented on the bus.

PSEN

PROGRAM STORE ENABLE: PSEN enables the external ROM data onto the Port 0

address/ data bus during fetch and MOVC operations. When internal ROM access is

performed, no PSEN strobe signal outputs from this pin. This pin also serves the

alternative function P4.6.

ALE

ADDRESS LATCH ENABLE: ALE is used to enable the address latch that separates

the address from the data on Port 0. This pin also serves the alternative function P4.5

RST

RESET: A high on this pin for two machine cycles while the oscillator is running resets

the device.

XTAL1

CRYSTAL1: This is the crystal oscillator input. This pin may be driven by an external

clock.

XTAL2

CRYSTAL2: This is the crystal oscillator output. It is the inversion of XTAL1.

V

SS

GROUND: Ground potential

V

DD

POWER SUPPLY: Supply voltage for operation.

P0.0

−P0.7 PORT 0: Port 0 is a bi-directional I/O port which also provides a multiplexed low order

address/data bus during accesses to external memory. The pins of Port 0 can be

individually configured to open-drain or standard port with internal pull-ups.

P1.0

−P1.7 PORT 1: Port 1 is a bi-directional I/O port with internal pull-ups. The bits have alternate

functions which are described below:

INT2

−INT9(P1.0−P1.7): External interrupt 2 to 9

P2.0

−P2.7 PORT 2: Port 2 is a bi-directional I/O port with internal pull-ups. This port also provides

the upper address bits for accesses to external memory.

P3.0

−P3.7 PORT 3: Port 3 is a bi-directional I/O port with internal pull-ups. The pins P3.4 to P3.7

can be configured with high sink current which can drive LED displays directly. All bits

have alternate functions, which are described below:

INT0 (P3.2) : External Interrupt 0

INT1

(P3.3) : External Interrupt 1

T0(P3.4) : Timer 0 External Input

T1(P3.5) : Timer 1 External Input

WR

(P3.6) : External Data Memory Write Strobe

RD

(P3.7) : External Data Memory Read Strobe

P4.0

−P4.6 PORT 4: A 6-bit bi-directional I/O port which is bit-addressable. Pins P4.0 to P4.3 are

available on 44-pin PLCC/QFP package. Pins P4.5 and P4.6 are the alternative

function corresponding to ALE and PSEN.