Rainbow Electronics MAX15020 User Manual

Page 15

MAX15020

2A, 40V Step-Down DC-DC Converter with

Dynamic Output-Voltage Programming

______________________________________________________________________________________

15

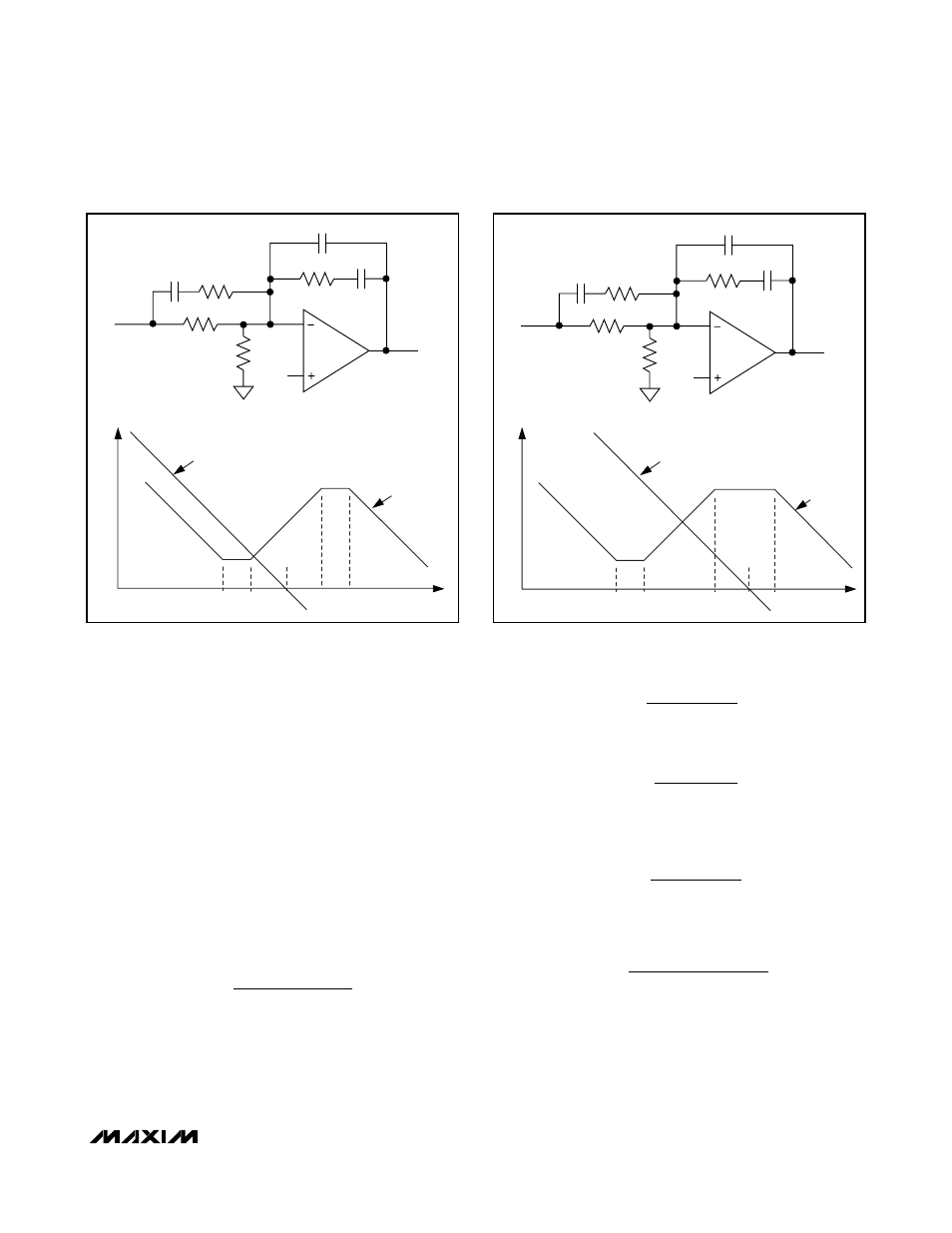

Compensation when f

C

> f

ZESR

For larger ESR capacitors such as tantalum and alu-

minum electrolytics, f

ZESR

can occur before f

C

. If f

ZESR

< f

C

, then f

C

occurs between f

P2

and f

P3

. f

Z1

and f

Z2

remain the same as before, however, f

P2

is now set

equal to f

ZESR

. The output capacitor’s ESR zero fre-

quency is higher than f

LC

but lower than the closed-

loop crossover frequency. The equations that define

the error amplifier’s poles and zeros (f

Z1

, f

Z2

, f

P1

, f

P2

,

and f

P3

) are the same as before. However, f

P2

is now

lower than the closed-loop crossover frequency. Figure

4 shows the error-amplifier feedback as well as its gain

response for circuits that use higher-ESR output capac-

itors (tantalum or aluminum electrolytic).

Pick a value for the feedback resistor R9 in Figure 4

(values between 1kΩ and 10kΩ are adequate).

C12 is then calculated as:

The error-amplifier gain between f

P2

and f

P3

is approxi-

mately equal to R9 / R6 (given that R6 << R7). R6 can

then be calculated as:

C11 is then calculated as:

Since R7 >> R6, R7 + R6 can be approximated as R7.

R7 is then calculated as:

f

P3

is set at 5 x f

C

. Therefore, C13 is calculated as:

Based on the calculations above, the following com-

pensation values are recommended when the switch-

ing frequency of DC-DC converter ranges from 100kHz

to 500kHz. (Note: The compensation parameters in

Figure 2 are strongly recommended if the switching

frequency is from 300kHz to 500kHz.)

C

C

C

R

f

P

13

12

2

12

9

1

3

=

Ч

Ч

Ч

−

π

R

f

C

LC

7

1

2

11

=

Ч

Ч

π

C

C

ESR

R

OUT

11

6

=

×

R

R

f

f

LC

C

6

9 10

2

2

=

Ч

Ч

C

f

R

LC

12

1

2

0 8

9

=

Ч

Ч

Ч

π

.

C12

SS

FB

f

Z1

f

Z2

f

C

f

P2

f

P3

CLOSED-LOOP

GAIN

FREQUENCY (Hz)

ERROR-

AMPLIFIER

GAIN

GAIN

(dB)

C13

C11

R9

V

OUT

COMP

R6

R7

R8

ERROR

AMPLIFIER

Figure 3. Error-Amplifier Compensation Circuit (Closed-Loop

and Error-Amplifier Gain Plot) for Ceramic Capacitors

C12

SS

f

Z1

f

Z2

f

P2

f

P3

CLOSED-LOOP

GAIN

ERROR-

AMPLIFIER

GAIN

C13

C11

R9

V

OUT

COMP

R6

R7

R8

ERROR

AMPLIFIER

f

C

FREQUENCY (Hz)

GAIN

(dB)

FB

Figure 4. Error-Amplifier Compensation Circuit (Closed-Loop

and Error-Amplifier Gain Plot) for Higher ESR Output Capacitors