Rainbow Electronics W78C438C User Manual

Page 8

W78C438C

- 8 -

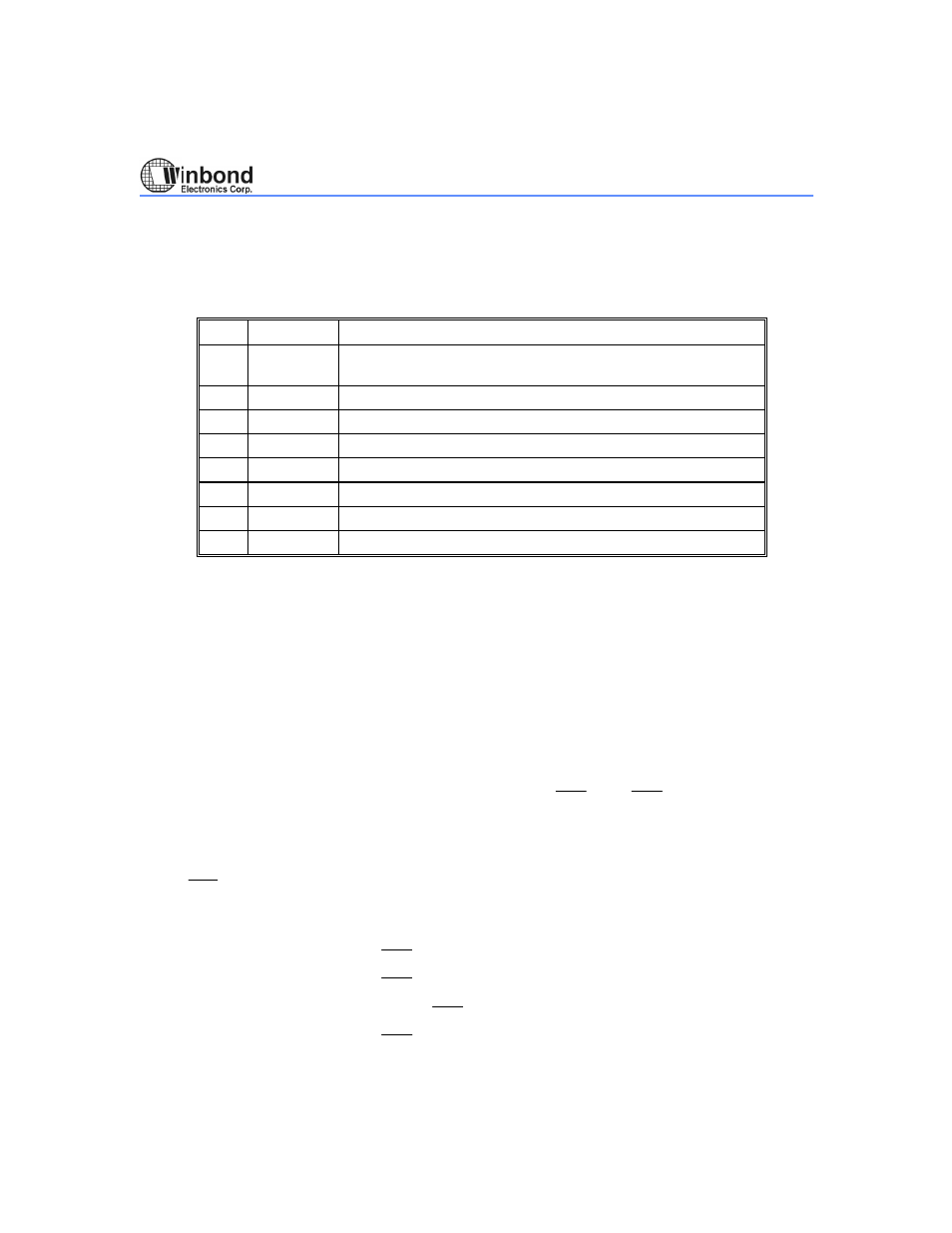

The EPMA register is a nonstandard 8-bit SFR at address 0A2H in the standard W78C32. To

read/write the EPMA register, one can use the "MOV direct" instruction or "read-modify-write"

instructions. Bits <6:4> of the EPMA register are reserved bits, and their output values are 111B if

they are read. The content of EPMA is 70H after a reset. The EPMA register does not support bit-

addressable instructions.

BIT

NAME

FUNCTION

7

EPMA7

EPMA7 = 0: 64 KB program/1 MB data memory space mode

EPMA7 = 1: memory-mapped chip select mode

6

EPMA6

Reserved

5

EPMA5

Reserved

4

EPMA4

Reserved

3

EPMA3

Value of AP7.3

2

EPMA2

Value of AP7.2

1

EPMA1

Value of AP7.1

0

EPMA0

Value of AP7.0

Table 1. Functional Description of EPMA Register

Additional I/O Port

The W78C438C provides one parallel I/O port, Port 8. Its function is the same as that of Port 1 in the

W78C31, except that it is mapped by the P8 register and is not bit-addressable. The P8 register is not

a standard register in the standard W78C32. Its address is at 0A6H. To read/write the P8 register, one

can use the "MOV direct" instruction or "read-modify-write" instructions.

[Example]: MOV

0A6H, A

; Output data via Port 8.

MOV

A, 0A6H

; Input data via Port 8.

Additional External Interrupt

The W78C438C provides two additional external interrupts,

INT2

and

INT3

, whose functions are

similar to those of external interrupts 0 and 1 in the W78C32. The functions (or the status) of these

interrupts are determined by (or shown by) the bits in the XICON (External Interrupt Control) register.

For details, see Table 2. The XICON register is bit-addressable but is not a standard register in the

standard 80C32. Its address is at 0C0H. To set/clear the bit of the XICON register, one can use the

"SETB(CLR) bit" instruction. For example, "SETB 0C2H" sets the EX2 bit of XICON. The interrupt

vector addresses and the priority polling sequence within the same level are shown in Table 3.

[Example].

SETB

0C0H

;

INT2

is falling-edge triggered.

SETB

0C3H

;

INT2

is high-priority.

SETB

0C2H

; Enable

INT2

.

CLR

0C4H

;

INT3

is low-level triggered.