Max5250, Table 1. serial-interface programming commands – Rainbow Electronics MAX5250 User Manual

Page 10

MAX5250

Figure 5 shows the serial-interface timing requirements.

The chip-select pin (

CS) must be low to enable the

DAC’s serial interface. When

CS is high, the interface

control circuitry is disabled.

CS must go low at least

t

CSS

before the rising serial clock (SCLK) edge to prop-

erly clock in the first bit. When

CS is low, data is

clocked into the internal shift register via the serial-data

input pin (DIN) on SCLK’s rising edge. The maximum

guaranteed clock frequency is 10MHz. Data is latched

into the appropriate MAX5250 input/DAC registers on

CS’s rising edge.

The programming command Load-All-DACs-From-Shift-

Register allows all input and DAC registers to be simul-

taneously loaded with the same digital code from the

input shift register. The no operation (NOP) command

leaves the register contents unaffected and is useful

when the MAX5250 is configured in a daisy chain (see

the

Daisy Chaining Devices

section). The command to

change the clock edge on which serial data is shifted

out of DOUT also loads data from all input registers to

their respective DAC registers.

Serial-Data Output (DOUT)

The serial-data output, DOUT, is the internal shift regis-

ter’s output. The MAX5250 can be programmed so that

data is clocked out of DOUT on SCLK’s rising edge

(Mode 1) or falling edge (Mode 0). In Mode 0, output

data at DOUT lags input data at DIN by 16.5 clock

cycles, maintaining compatibility with Microwire,

SPI/QSPI, and other serial interfaces. In Mode 1, output

data lags input data by 16 clock cycles. On power-up,

DOUT defaults to Mode 0 timing.

User-Programmable Logic Output (UPO)

The user-programmable logic output, UPO, allows an

external device to be controlled via the MAX5250 serial

interface (Table 1).

Low-Power, Quad, 10-Bit Voltage-Output DAC

with Serial Interface

10

______________________________________________________________________________________

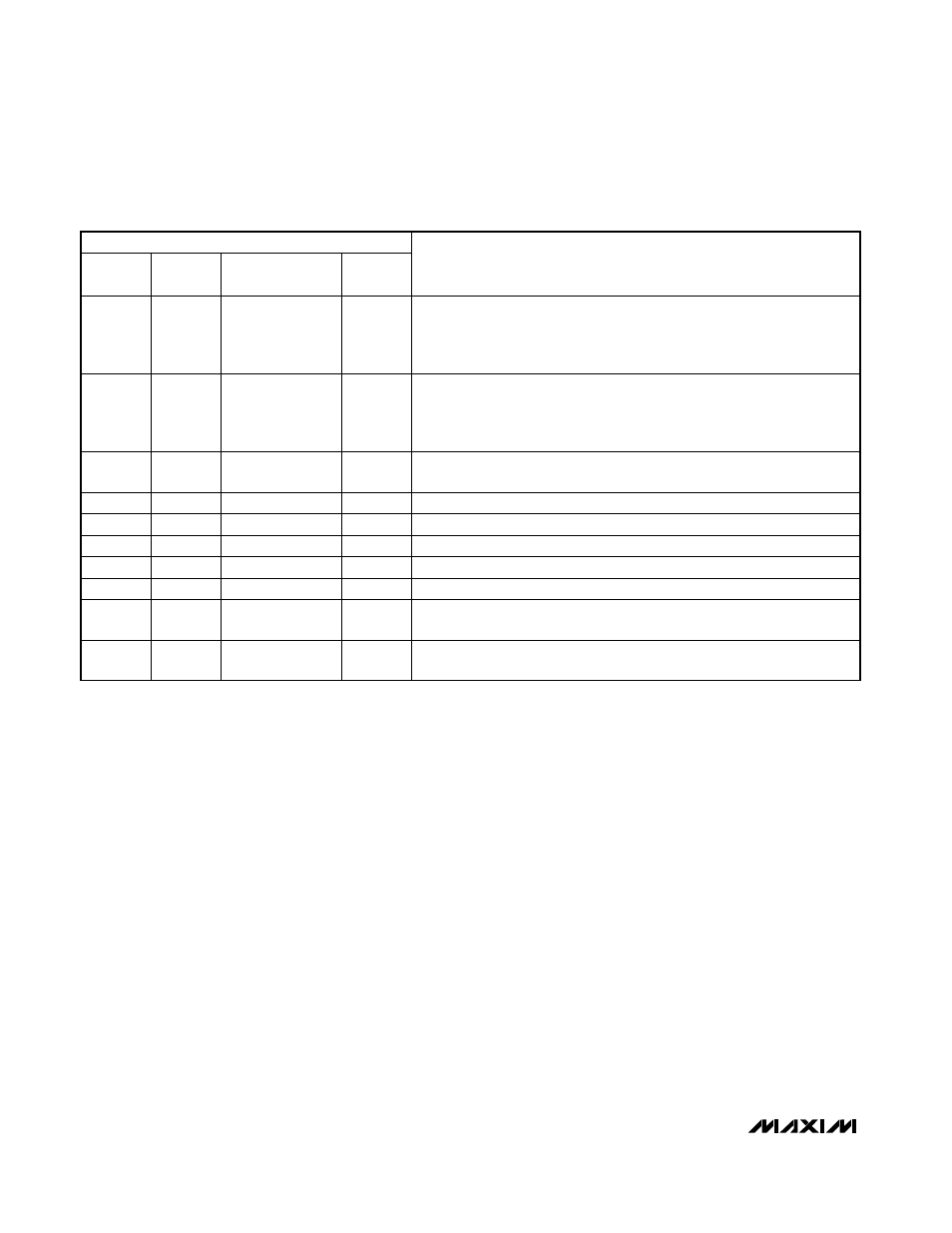

Table 1. Serial-Interface Programming Commands

“X” = Don’t care

16-BIT SERIAL WORD

FUNCTION

A1

A0

C1

C0

D9.................D0

MSB.............LSB

S1

S0

0

0

0

1

1

0

1

1

0

1

0

1

0

1

0

1

10-bit DAC data

10-bit DAC data

10-bit DAC data

10-bit DAC data

0

0

0

0

0

0

0

0

Load input register A; DAC registers unchanged.

Load input register B; DAC registers unchanged.

Load input register C; DAC registers unchanged.

Load input register D; DAC registers unchanged.

0

0

0

1

1

0

1

1

1

1

1

1

1

1

1

1

10-bit DAC data

10-bit DAC data

10-bit DAC data

10-bit DAC data

0

0

0

0

0

0

0

0

Load input register A; all DAC registers updated.

Load input register B; all DAC registers updated.

Load input register C; all DAC registers updated.

Load input register D; all DAC registers updated.

0

1

0

0

XXXXXXXXXX

X

X

Update all DAC registers from their respective input registers (also exit

shutdown mode).

1

0

0

0

10-bit DAC data

0

0

Load all DAC registers from shift register (also exit shutdown mode).

1

1

0

0

XXXXXXXXXX

X

X

Enter shutdown mode (provided

PDL = 1).

0

0

1

0

XXXXXXXXXX

X

X

UPO goes low (default).

0

1

1

0

XXXXXXXXXX

X

X

UPO goes high.

0

0

0

0

XXXXXXXXXX

X

X

No operation (NOP) to DAC registers

1

1

1

0

XXXXXXXXXX

X

X

Mode 1, DOUT clocked out on SCLK’s rising edge. All DAC registers

updated.

1

0

1

0

XXXXXXXXXX

X

X

Mode 0, DOUT clocked out on SCLK’s falling edge. All DAC registers

updated (default).