W78c54 – Rainbow Electronics W78C54 User Manual

Page 11

W78C54

Publication Release Date: December 1997

- 11 -

Revision A2

TR1: Timer 1 run control bit. Set/cleared by software to turn timer/counter on or off.

TF0: Timer 0 overflow flag. Set by hardware on timer/counter overflow. Cleared by hardware when

processor vectors to interrupt routine.

TR0: Timer 0 run control bit. Set/cleared by software to turn timer/counter on or off.

IE1: Interrupt 1 edge flag. Set by hardware when external interrupt edge detected. Cleared when

interrupt processed.

IT1: Interrupt 1 type control bit. Set/cleared by software to specify falling edge/low level triggered

external interrupt.

IE0: Interrupt 0 edge flag. Set by hardware when external interrupt edge detected. Cleared when

interrupt processed.

IT0: Interrupt 0 type control bit. Set/cleared by software to specify falling edge/low level triggered

external interrupt.

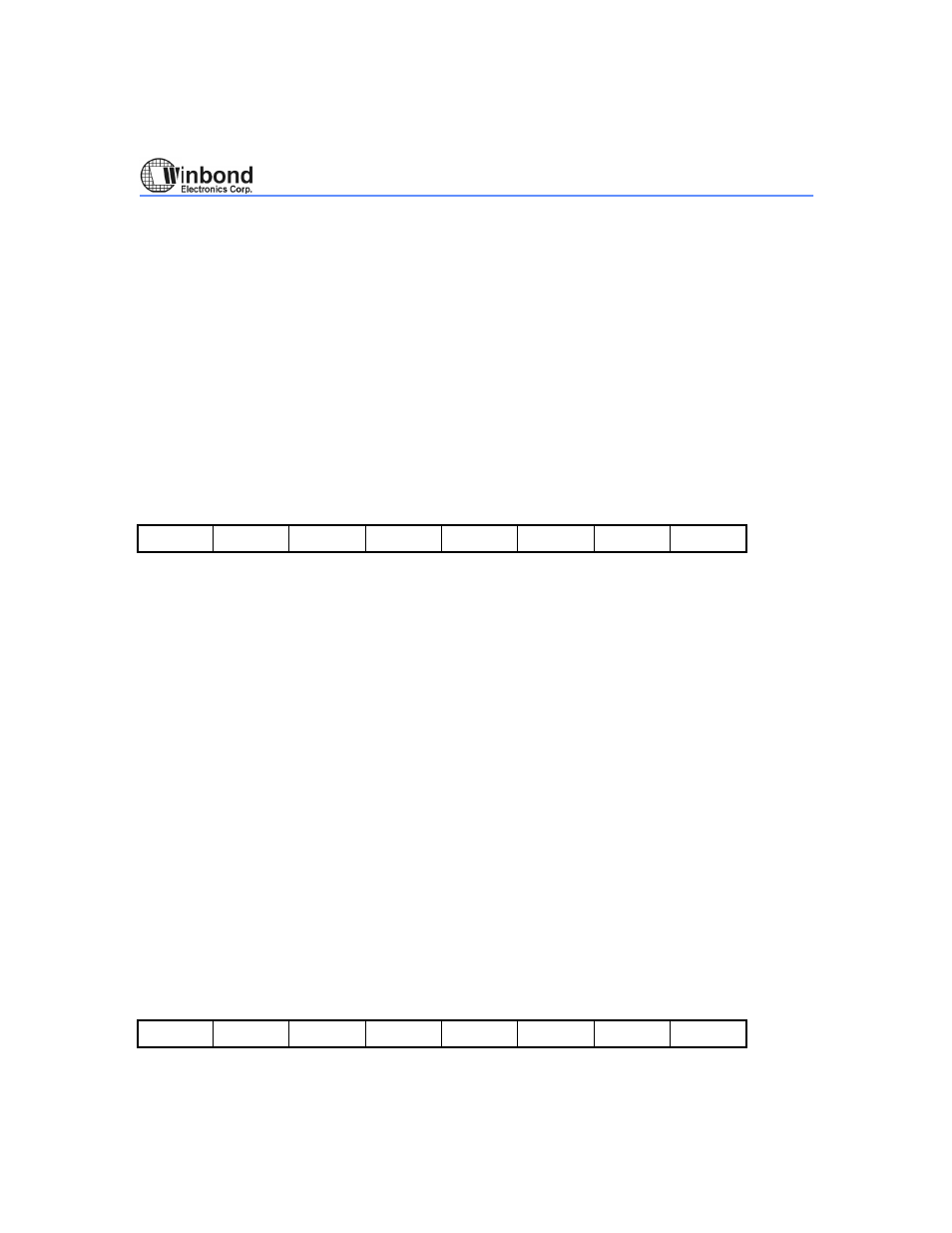

***T2CON - Timer 2 Control (C8H)

TF2

EXF2

RCLK

TCLK

EXEN2

TR2

C//T

CP//RL2

TF2:

Timer 2 overflow flag. Set by a Timer 2 overflow and must be cleared by software. TF2 will

not be set when RCLK = 1 or TCLK = 1.

EXF2:

Timer2 external flag. Set when either a capture or reload is caused by a negative transition

on T2EX and EXEN2 = 1. When Timer 2 interrupt is enabled, EXF2 = 1 will cause the CPU

to vector to the Timer 2 interrupt routine. EXF2 must be cleared by software.

RCLK:

Receive clock flag. RCLK = 1 causes the serial port to use Timer 2 overflow pulses for its

receive clock in mode 1 and 3. RCLK = 0 causes Timer 1 overflow to be used for the

receive clock.

TCLK:

Transmit clock flag. TCLK = 1 causes the serial port to use Timer 2 overflow pulses for its

transmit clock in mode 1 and 3. TCLK = 0 causes Timer 1 overflow to be used for the

transmit clock.

EXEN2: Timer 2 external enable flag. EXEN2 = 1 allows a capture or reload to occur as a result of a

negative transition on T2EX if Timer 2 is not used to clock the serial port. EXEN2 = 0

causes

Timer 2 to ignore events at T2EX.

TR2:

TR2 = 1/0: turns on/off Timer 2.

C//T:

Timer or Counter select. Set 1/0 for external event counter(falling edge triggered)/inter

timer.

CP//RL2: Capture/reload flag.

*Reduced EMI Mode

The AO bit in the AUXR register, when set, disables the ALE output.

***AUXR - Auxiliary Register (8EH)

-

-

-

-

-

-

-

AO

AO: Turn off ALE output.