Pin arrangement, Pin description – Renesas HD49335HNP User Manual

Page 2

HD49335NP/HNP

Rev.1.0, Feb.12.2004, page 2 of 29

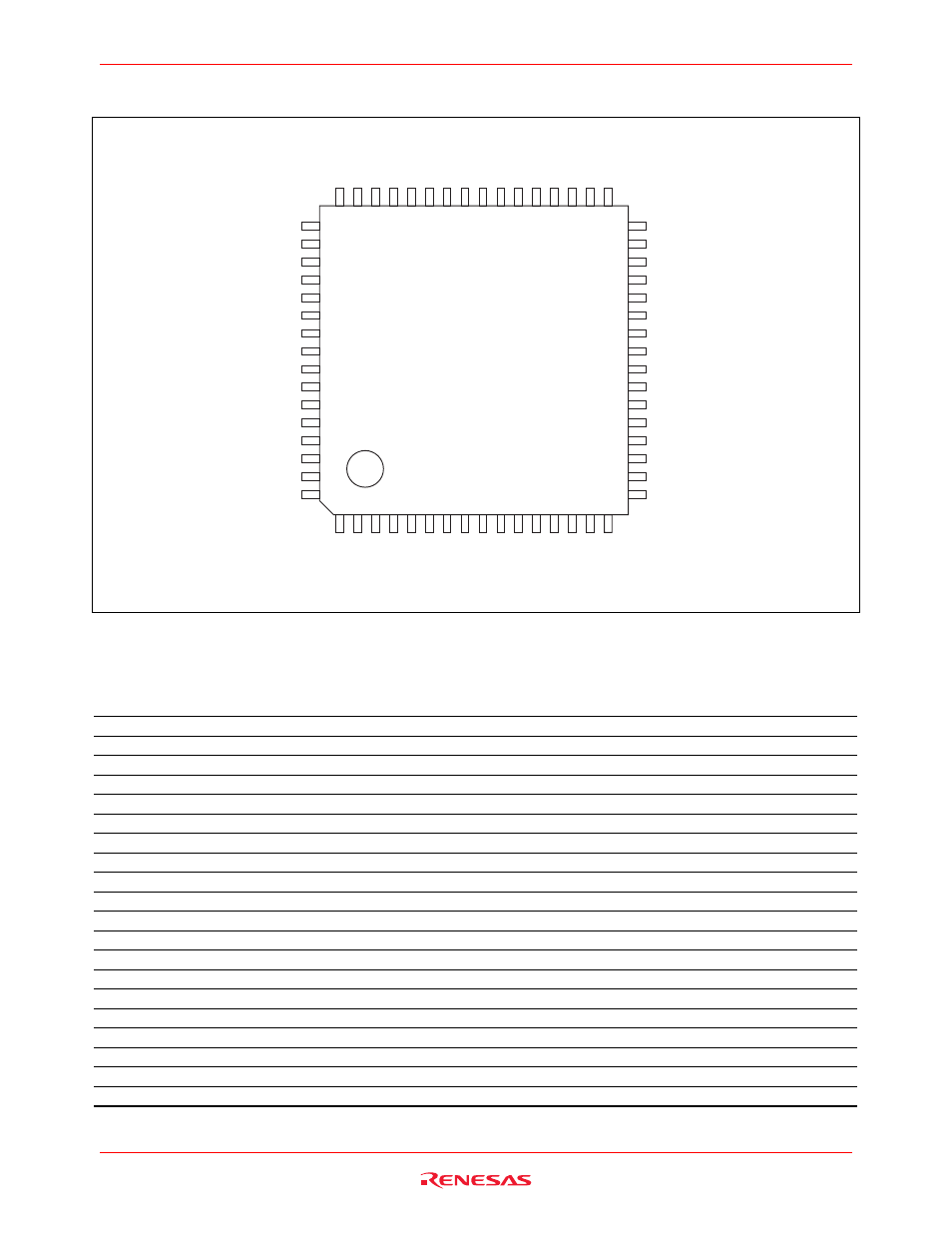

Pin Arrangement

48 47

39

46 45 44 43 42 41 40

38

36 35 34

37

1 2

10

3 4 5 6 7 8 9

11 12 13 14 15

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

(Top view)

AV

DD

BLKC

CDS_in

AV

DD

BLKFB

BLKSH

AV

SS

Test2

Test1

DLL_C

DV

DD

1

MON

41cont

CS

SDATA

SCK

XV3

XV2

XV1

DV

DD

3

DV

DD

4

1/4clk_o

H2A

DV

SS

4

DV

SS

4

1/2clk_o

H1A

DV

DD

4

DV

DD

3

RG

Reset

VD_in

VRM

VRT

VRB

BIAS

ADC_in

AV

SS

DV

SS

3

STROB

SUB_PD

SUB_SW

XSUB

CH4

CH3

CH2

CH1

XV4

ID

DV

SS

1,2

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

DV

DD

2

DV

SS

3

CLK_in

HD_in

33

16

Pin Description

Pin No.

Symbol

Description

I/O

Analog(A) or

Digital(D)

Remarks

1

ID

Odd/even number line detecting pulse output pin

O

D

2 mA/10 pF

2 DV

SS

1,2

CDS Digital ground + ADC output buffer ground (0 V)

—

D

3 to 12

D0 to D9

Digital output (D0; LSB, D9; MSB)

O

D

2 mA/10 pF

13 DV

DD

2

ADC output buffer power supply (3 V)

—

D

14 DV

SS

3

General ground for TG (0 V)

—

D

15

CLK_in

CLK input (max 72 MHz)

I

D

16 HD_in

HD

input

I/O

D

17 VD_in

VD

input

I/O

D

18

Reset

Hardware reset (for DLL reset)

I

D

Schmitt trigger

19

RG

Reset gate pulse output

O

D

3 mA/10 pF

20 DV

DD

3

General power supply for TG (3 V)

—

D

21 DV

DD

4

H1 buffer power supply (3 V)

—

D

22

H1A

H.CCD transfer pulse output-1A

O

D

30 mA/165 pF

23

1/2clk_o

CLK_in 2 divided output. 3 divided output at 3 divided mode

O

D

2 mA/10 pF

24 DV

SS

4

H1 buffer ground (0 V)

—

D

25 DV

SS

4

H1 buffer ground (0 V)

—

D

26

H2A

H.CCD transfer pulse output-2A

O

D

30 mA/165 pF

27

1/4clk_o

CLK_in 4 divided output. 6 divided output at 3 divided mode

O

D

2 mA/10 pF

28 DV

DD

4

H2 buffer power supply (3 V)

—

D

29 DV

DD

3

General power supply for TG (3 V)

—

D