Summit S93WD462 User Manual

Page 8

8

S93WD462/S93WD463

2029 2.2 1/23/01

SUMMIT MICROELECTRONICS, Inc.

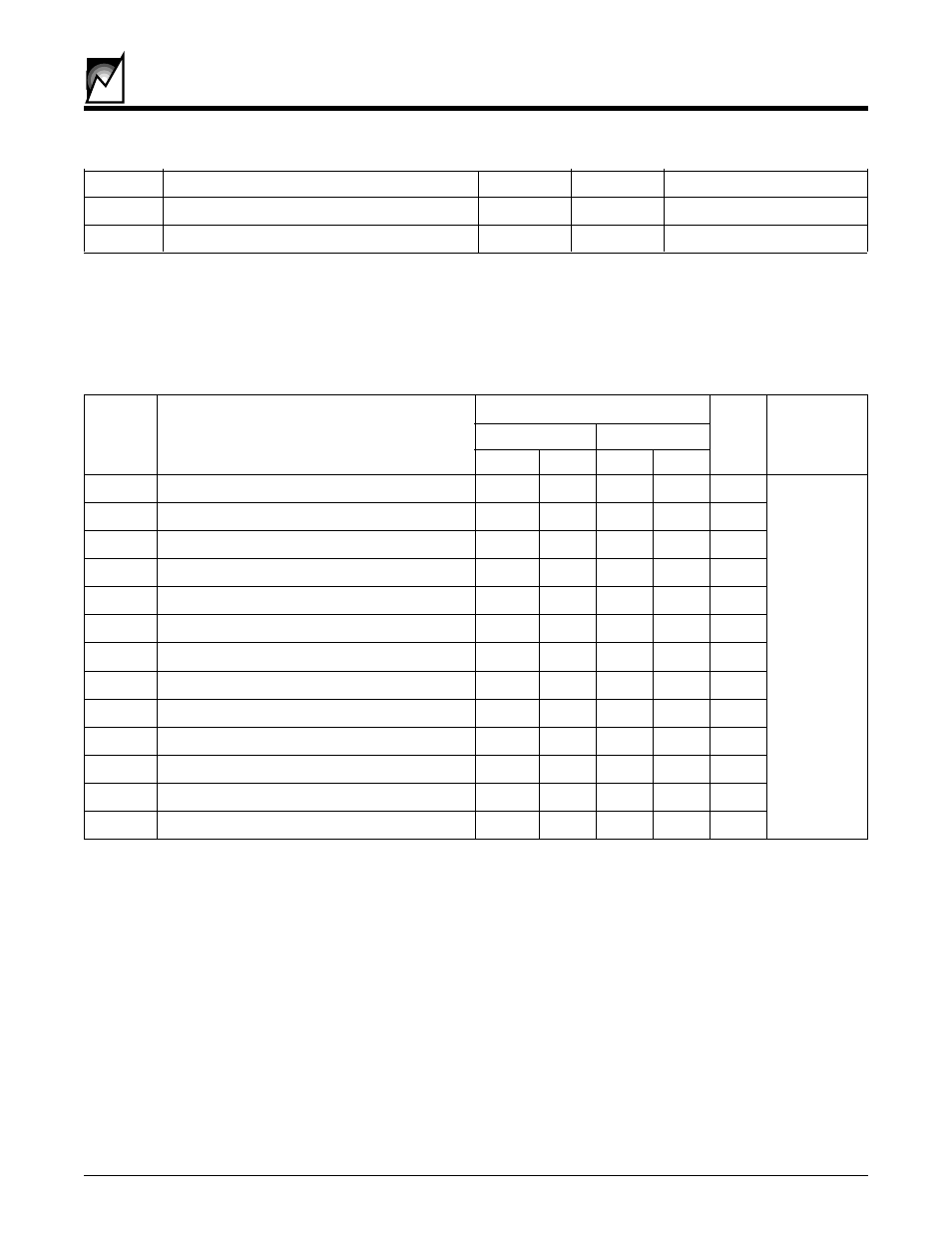

Limits

V

CC

=2.7V-4.5V V

CC

=4.5V-5.5V

Test

SYMBOL PARAMETER

Min.

Max.

Min.

Max.

UNITS

Conditions

t

CSS

CS Setup Time

100

50

ns

t

CSH

CS Hold Time

0

0

ns

V

IL

= 0.45V

t

DIS

DI Setup Time

200

100

ns

V

IH

= 2.4V

t

DIH

DI Hold Time

200

100

ns

C

L

= 100pF

t

PD1

Output Delay to 1

0.5

0.25

µs

V

OL

= 0.8V

t

PD0

Output Delay to 0

0.5

0.25

µs

V

OH

= 2.0v

t

HZ

(1)

Output Delay to High-Z

200

100

ns

t

EW

Program/Erase Pulse Width

10

10

ms

t

CSMIN

Minimum CS Low Time

0.5

0.25

µs

t

SKHI

Minimum SK High Time

0.5

0.25

µs

t

SKLOW

Minimum SK Low Time

0.5

0.25

µs

t

SV

Output Delay to Status Valid

0.5

0.25

µs

C

L

= 100pF

SK

MAX

Maximum Clock Frequency

DC

500

DC

1000

KHZ

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

A.C. CHARACTERISTICS (over recommended operating conditions unless otherwise specified)

C

L

= 100pF

2029 PGM T6.0

PIN CAPACITANCE

Symbol

Test

Max.

Units

Conditions

C

OUT

(1)

OUTPUT CAPACITANCE (DO)

5

pF

V

OUT

=OV

C

IN

(1)

INPUT CAPACITANCE (CS, SK, DI, ORG)

5

pF

V

IN

=OV

2029 PGM T4.0