Table 2.2 eeprom pins, Table 2.3 jtag pins, Table 2.2 eeprom pins table 2.3 jtag pins – SMSC LAN9500 User Manual

Page 13: Datasheet

Hi-Speed USB 2.0 to 10/100 Ethernet Controller

Datasheet

SMSC LAN9500/LAN9500i

13

Revision 1.7 (10-02-08)

DATASHEET

Note 2.2

Configuration strap values are latched on power-on reset and system reset. Configuration

straps are identified by an underlined symbol name. Signals that function as configuration

straps must be augmented with an external resistor when connected to a load.

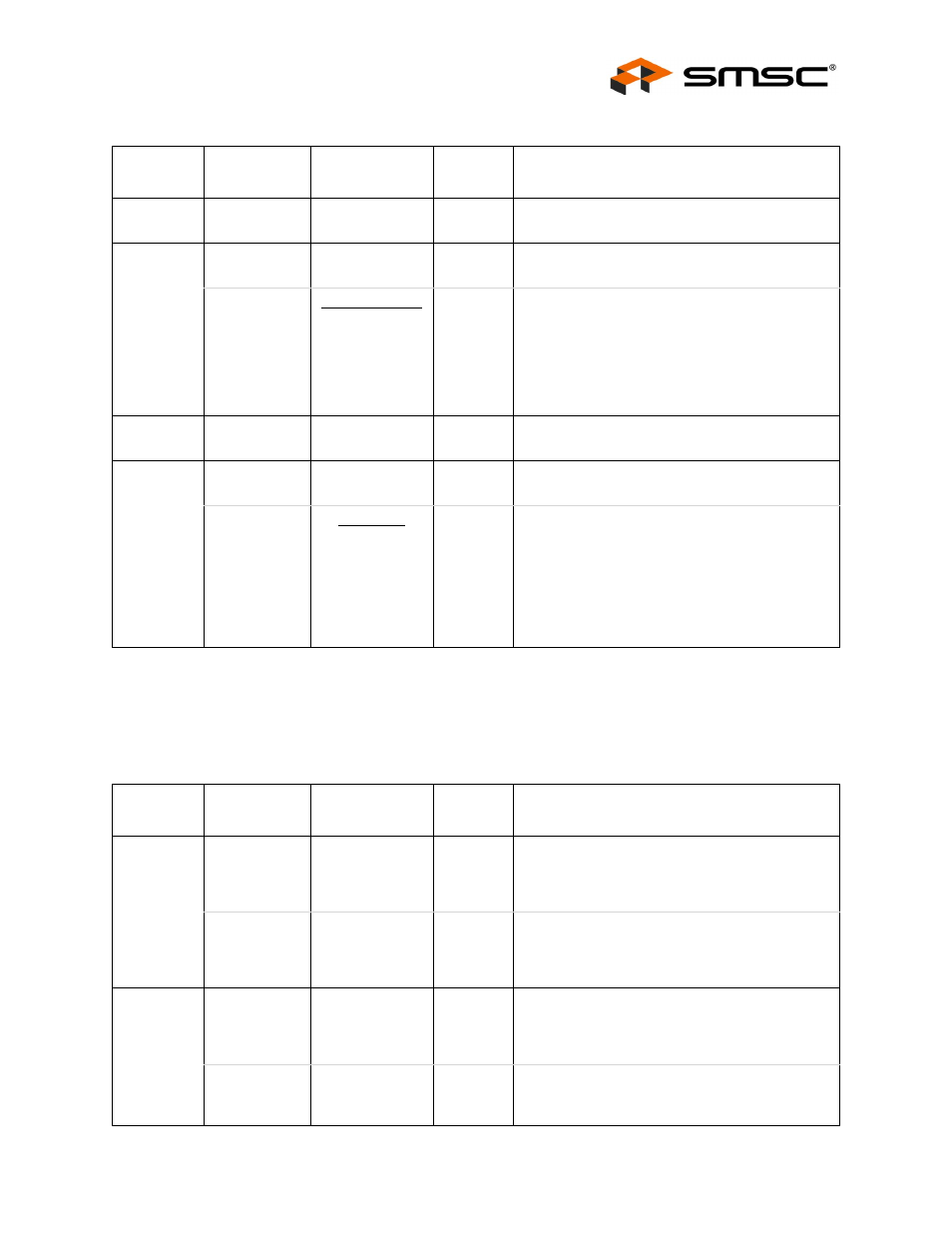

Table 2.2 EEPROM Pins

NUM PINS

NAME

SYMBOL

BUFFER

TYPE

DESCRIPTION

1

EEPROM

Data In

EEDI

IS

(PD)

EEPROM Data In: This pin is driven by the

EEDO output of the external EEPROM.

1

EEPROM

Data Out

EEDO

O8

(PU)

EEPROM Data Out: This pin drives the EEDI

input of the external EEPROM.

Auto-MDIX

Enable

Configuration

Strap

AUTOMDIX_EN

IS

(PU)

Auto-MDIX Enable Configuration Strap:

Determines the default Auto-MDIX setting.

0 = Auto-MDIX is disabled.

1 = Auto-MDIX is enabled.

See

for more information on

configuration straps.

1

EEPROM

Chip Select

EECS

O8

EEPROM chip select: This pin drives the chip

select output of the external EEPROM.

1

EEPROM

Clock

EECLK

O8

(PD)

EEPROM Clock: This pin drives the EEPROM

clock of the external EEPROM.

Power Select

Configuration

Strap

PWR_SEL

IS

(PD)

Power Select Configuration Strap: Determines

the default power setting when no EEPROM is

present.

0 = The LAN9500/LAN9500i is bus powered.

1 = The LAN9500/LAN9500i is self powered.

See

for more information on

configuration straps.

Table 2.3 JTAG Pins

NUM PINS

NAME

SYMBOL

BUFFER

TYPE

DESCRIPTION

1

JTAG Test

Port Reset

(Internal PHY

Mode)

nTRST

IS

(PU)

JTAG Test Port Reset (Active-Low): In internal

PHY mode, this pin functions as the JTAG test

port reset input.

Receive Data

0

(External

PHY Mode)

RXD0

IS

(PD)

Receive Data 0: In external PHY mode, this pin

functions as the receive data 0 input from the

external PHY.

1

JTAG Test

Data Out

(Internal PHY

Mode)

TDO

O8

JTAG Data Output: In internal PHY mode, this

pin functions as the JTAG data output.

PHY Reset

(External

PHY Mode)

nPHY_RST

O8

PHY Reset (Active-Low): In external PHY

mode, this pin functions as the PHY reset output.