4 card configuration – SanDisk CompactFlash Extreme III User Manual

Page 38

Interface Description

SanDisk CompactFlash Card OEM Product Manual

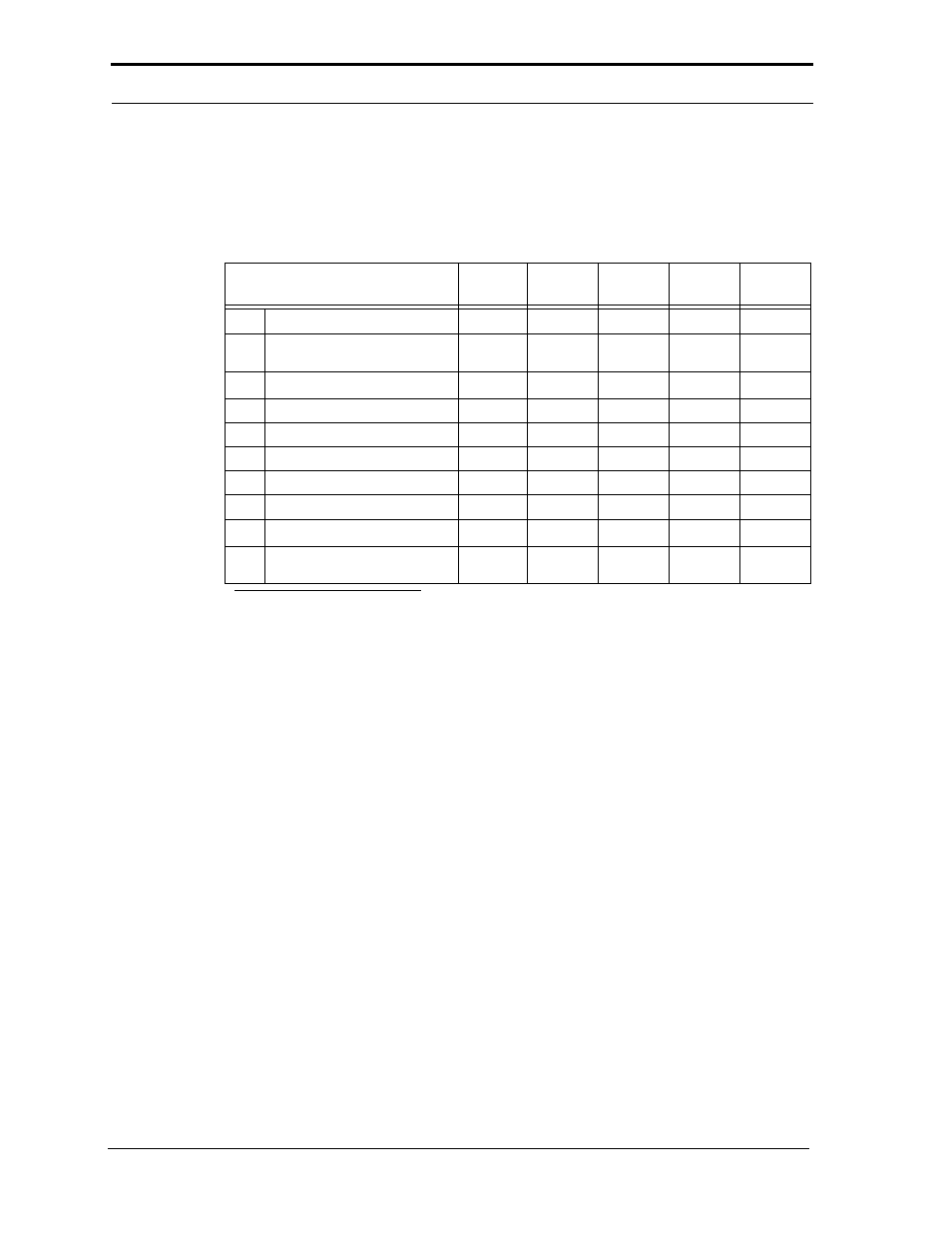

The PIO data transfer parameters are defined in Table 3-16.

NOTE

: SanDisk CompactFlash Memory cards do not assert an -IORDY

signal.

Table 3-16

PIO Data Transfer to/from Device

PIO Timing Parameters

Mode 0

(ns)

Mode 1

(ns)

Mode 2

(ns)

Mode 3

(ns)

Mode 4

(ns)

t

0

a

Cycle time (min.)

600

383

240

180

120

t

1

Address valid to IORD-/IOWR- setup

(min.)

70

50

30

30

25

t

2

a

IORD-/IOWR- pulse width 16-bit (min.)

165

125

100

80

70

t

2ia

IORD-/IOWR- recovery time (min.)

---

---

---

70

25

t

3

IOWR- data setup (min.)

60

45

30

30

20

t

4

IOWR- data hold (min.)

30

20

15

10

10

t

5

IORD- data setup (min.)

50

35

20

20

20

t

6

IORD- data hold (min.)

5

5

5

5

5

t

6z

b

IORD- data tri-state (max.)

30

30

30

30

30

t

9

IORD-/IOWR- to address valid hold

(min.)

20

15

10

10

10

a. t

0

is the minimum total cycle time, t

2

is the minimum command active time, and t

2i

is the minimum

command recovery time or command inactive time. The actual cycle time equals the sum of the

actual command active time and the actual command inactive time. The three timing requirements of

t

0

, t

2

, and t

2i

shall be met. The minimum total cycle time requirements are greater than the sum of t

2

and t

2i

. This means a host implementation may lengthen either or both t

2

or t

2i

to ensure that t

0

is

equal to or greater than the value reported in the devices IDENTIFY DEVICE data. A device imple

mentation shall support any legal host implementation.

b. This parameter specifies the time from the negation edge of /IORD to the time that the data bus is no

longer driven by the device (tri-state).

3.4

Card Configuration

SanDisk CompactFlash Memory cards are identified by appropriate information in the Card

Information Structure (CIS). The configuration registers are used to coordinate the I/O spaces

and the interrupt level of cards that are located in the system.

02/07, Rev. 12.0

3-20

© 2007 SanDisk Corporation