Block diagram, Figure 1 lpc47n217n block diagram, Product preview – SMSC LPC47N217N User Manual

Page 4

56-Pin Super I/O with LPC Interface

Revision 0.3 (01-23-09)

4

SMSC LPC47N217N 56QFN

PRODUCT PREVIEW

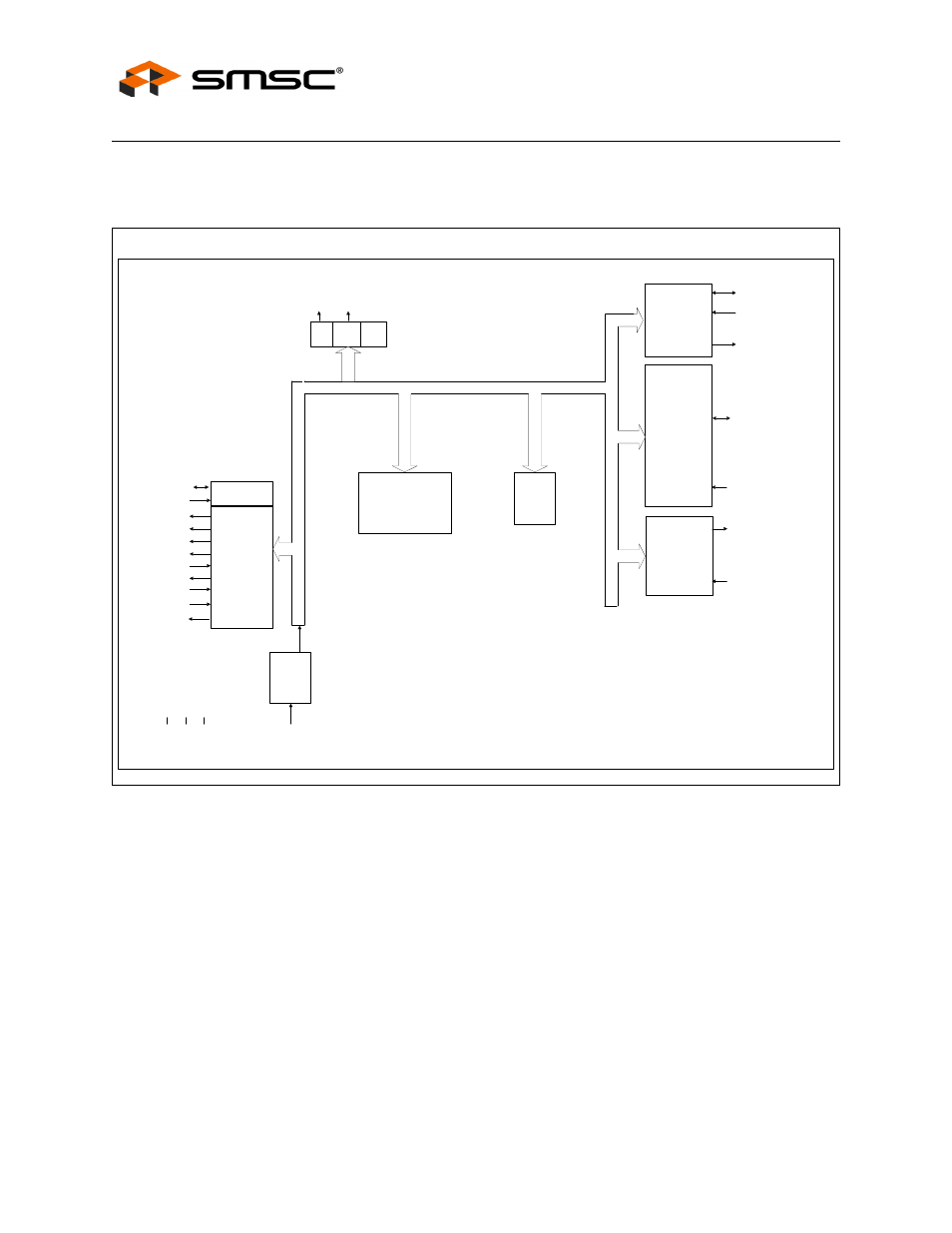

Block Diagram

Figure 1 LPC47N217N Block Diagram

TXD1, nRTS1, nDTR1

SER_IRQ

PCI_CLK

Vcc GND

IO_PME#

Denotes Multifunction Pins

SERIAL

IRQ

LPC BUS

INTERFACE

V

TR

CLOCK

GEN

CLOCKI

SMI PME WDT

*

16C550

COMPATIBLE

SERIAL

PORT 1

nCTS1, RXD1,

nDSR1, nDCD1, nRI1

CONFIGURATION

REGISTERS

GENERAL

PURPOSE

I/O

GP10, GP11,

GP12*, GP13*,

GP14*,

GP23,

GP4[1:7]

MULTI-MODE

PARALLEL

PORT

PD[0:7],

BUSY, SLCT,

PE, nERROR, nACK

nSLCTIN, nALF

nINIT, nSTROBE

CONTROL, ADDRESS, DATA

LAD0

LAD1

LAD2

LAD3

LFRAME#

LDRQ#

LPCPD#

PCI_RESET#

ACPI

BLOCK

IO_SMI#*

CLKRUN#

IRQIN1*, IRQIN2*