Sony Ericsson GS64 User Manual

Page 68

LZT 123 1836

68

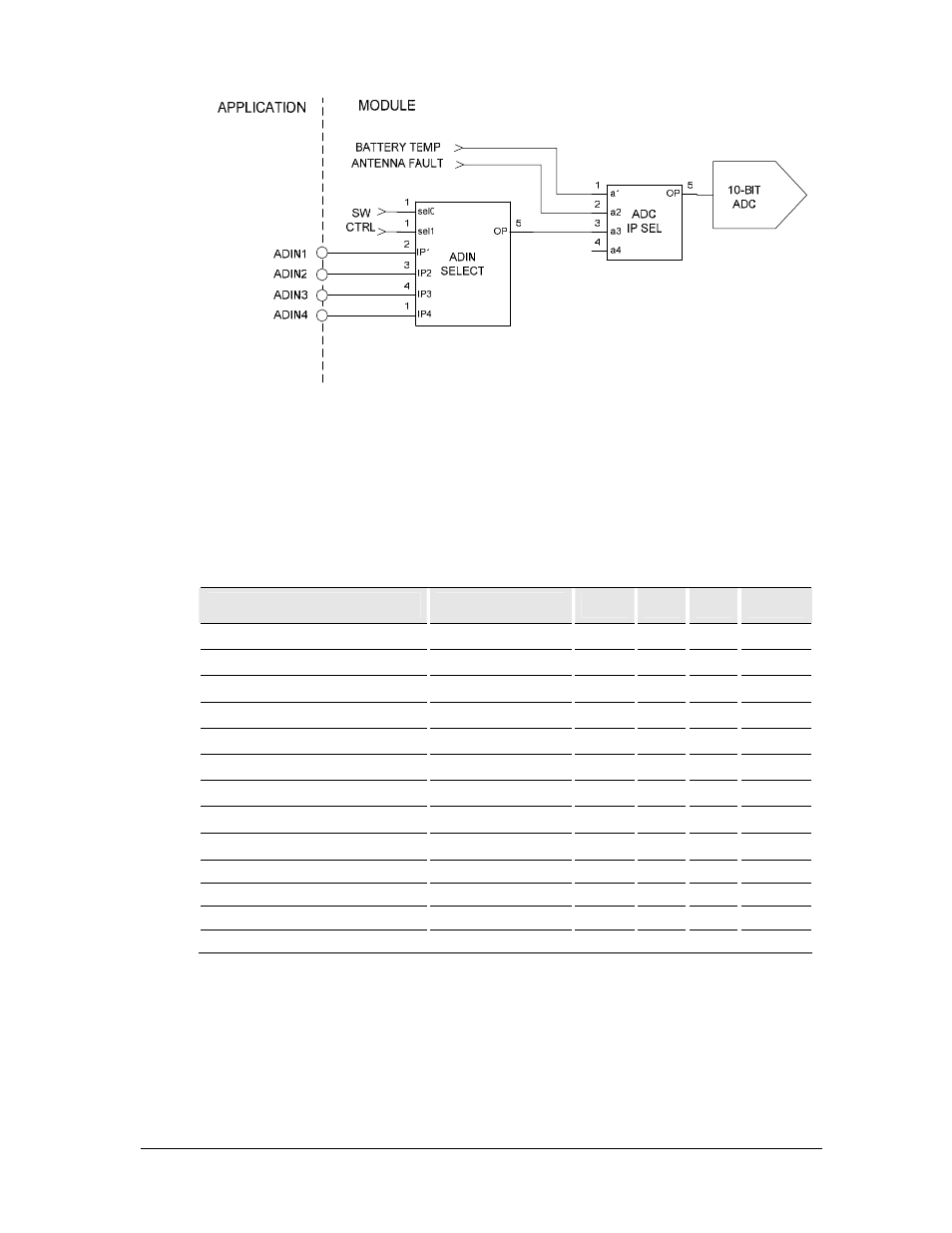

Figure 5.18-1 ADC sharing arrangement

ADC sampling frequency and sampling source selection can be set up and controlled

with AT-commands by the user. ADC samples requires up to 5 clock (ADCLK) cycles

to process. The ADC also performs some system-level sampling. These two factors

limit the maximum practical sampling rate to around 12ksps.

Table 5.18-1 ADC Interface Characteristics

Parameter

Condition

Min

Typ Max

Unit

Resolution

10

bit

Coding: Unsigned Magnitude

000

3FF

Hex

Differential Nonlinearity

–1

1

lsb

Integral Nonlinearity

–10

10

lsb

Full-scale Error

–3

3

%

Offset Error

–14

14

lsb

Conversion Gain*

421

lsb/V

Conversion Intercept*

–9

lsb

Low-level Input Voltage

ADC output=000h

High-level Input Voltage

ADC output=3FFh

2.45

2.59

V

ADC Clock (ADCLK)

260

325 390

kHz

ADC Conversion Time

12

ADCLK

ADC Sample Delay

5

ADCLK