Sony E01X23A41 User Manual

Page 5

– 5 –

ICX423AL

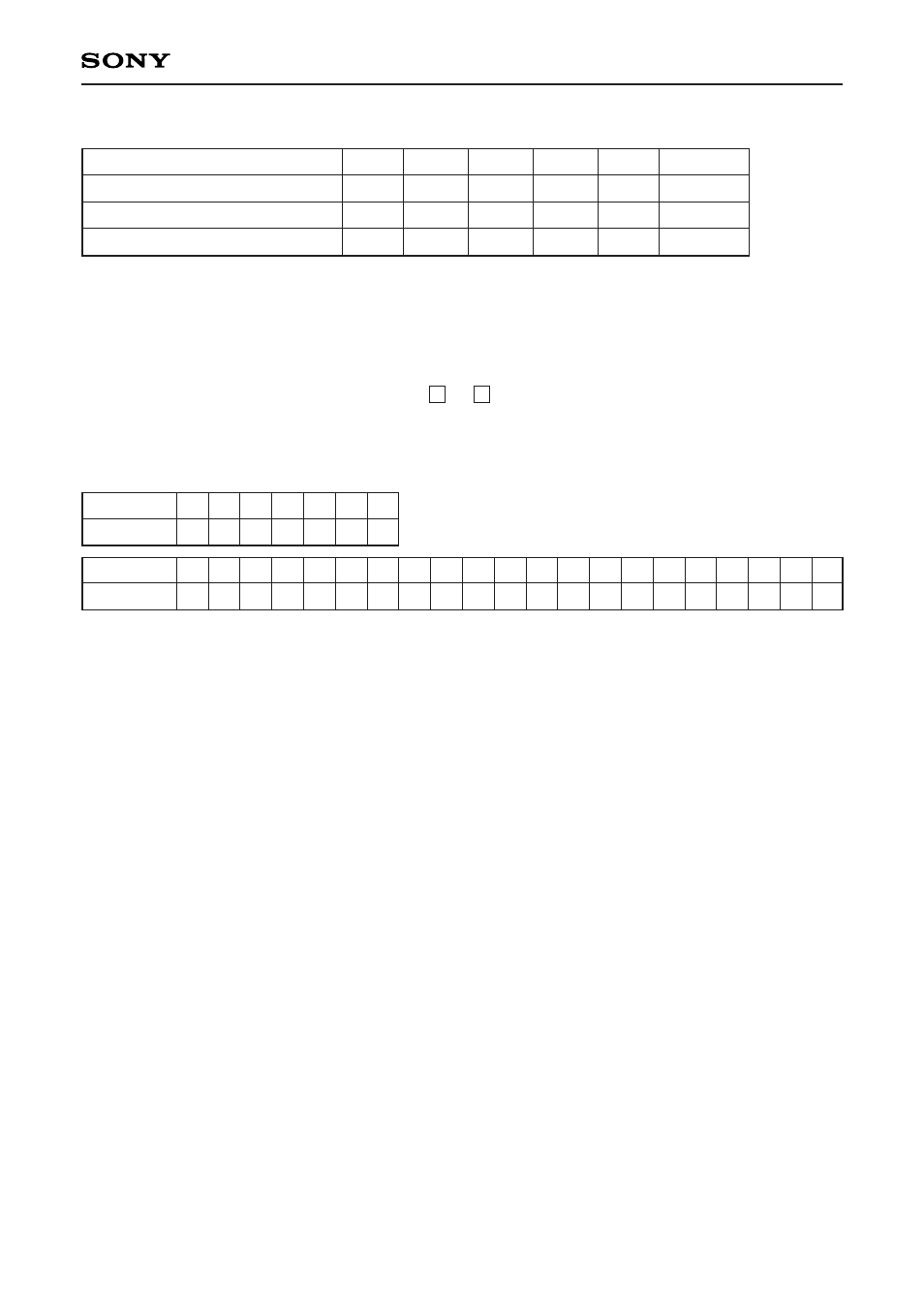

DC Characteristics

Output amplifier drain current

Input current

Input current

Item

I

DD

I

IN1

I

IN2

Symbol

6

Min.

Unit

Remarks

Typ.

Max.

mA

µA

µA

1

10

∗

2

Indications of substrate voltage (V

SUB

) and reset gate clock voltage (V

RGL

) setting value

The setting value of the substrate voltage and reset gate clock voltage are indicated on the back of the

image sensor by a special code. Adjust the substrate voltage (V

SUB

) and reset gate clock voltage (V

RGL

) to

the indicated voltage. The adjustment precision is ±3%.

V

SUB

code — one character indication

V

RGL

code — one character indication

↑

↑

V

RGL

code

V

SUB

code

"Code" and optimal setting correspond to each other as follows.

→

V

RGL

= 2.0V

V

SUB

= 12.0V

V

SUB

code

Optimal setting

D

9.0

∗

4

∗

5

E

9.5

f

10.0

G

10.5

h

11.0

J

11.5

K

12.0

L

12.5

m

13.0

N

13.5

P

14.0

Q

14.5

R

15.0

S

15.5

T

16.0

U

16.5

V

17.0

W

17.5

X

18.0

Y

18.5

Z

19.0

V

RGL

code

Optimal setting

1

0

2

0.5

3

1.0

4

1.5

5

2.0

6

2.5

7

3.0

∗

3

This must no exceed the V

VL

voltage of the vertical clock waveform.

∗

4

1) Current to each pin when 20V is applied to V

DD

, RD, V

OUT

, V

SS

, HIS and SUB pins, while pins that are

not tested are grounded.

2) Current to each pin when 20V is applied sequentially to V

φ

1

, V

φ

2

, V

φ

3

and V

φ

4

pins, while pins that are

not tested are grounded. However, 20V is applied to SUB pin.

3) Current to each pin when 15V is applied sequentially to H

φ

1

, H

φ

2

, RG and V

GG

pins, while pins that are

not tested are grounded. However, 15V is applied to SUB pin.

4) Current to V

L

pin when 30V is applied to V

φ

1

, V

φ

3

, HIS, V

DD

, RD and V

OUT

pins or when, 24V is applied

to RG pin or when, 20V is applied to V

φ

2

, V

φ

4

, V

GG

, V

SS

, H

φ

1

and H

φ

2

pins, while V

L

pin is grounded.

However, GND and SUB pins are left open.

∗

5

Current to SUB pin when 55V is applied to SUB pin, while pins that are not tested are grounded.