FUJITSU MB90890 User Manual

Page 3

N

ew Products

MB90890 Series

13

FIND Vol.21

No.1

2003

Delayed interruption generating module

8/10-bit A/D converter: 8 channels

Address match detection function

Input level changeable by software

■

Package: FPT-48P-M26

Features of Dual-Operation

Flash Memory-Integrated

Microcontrollers

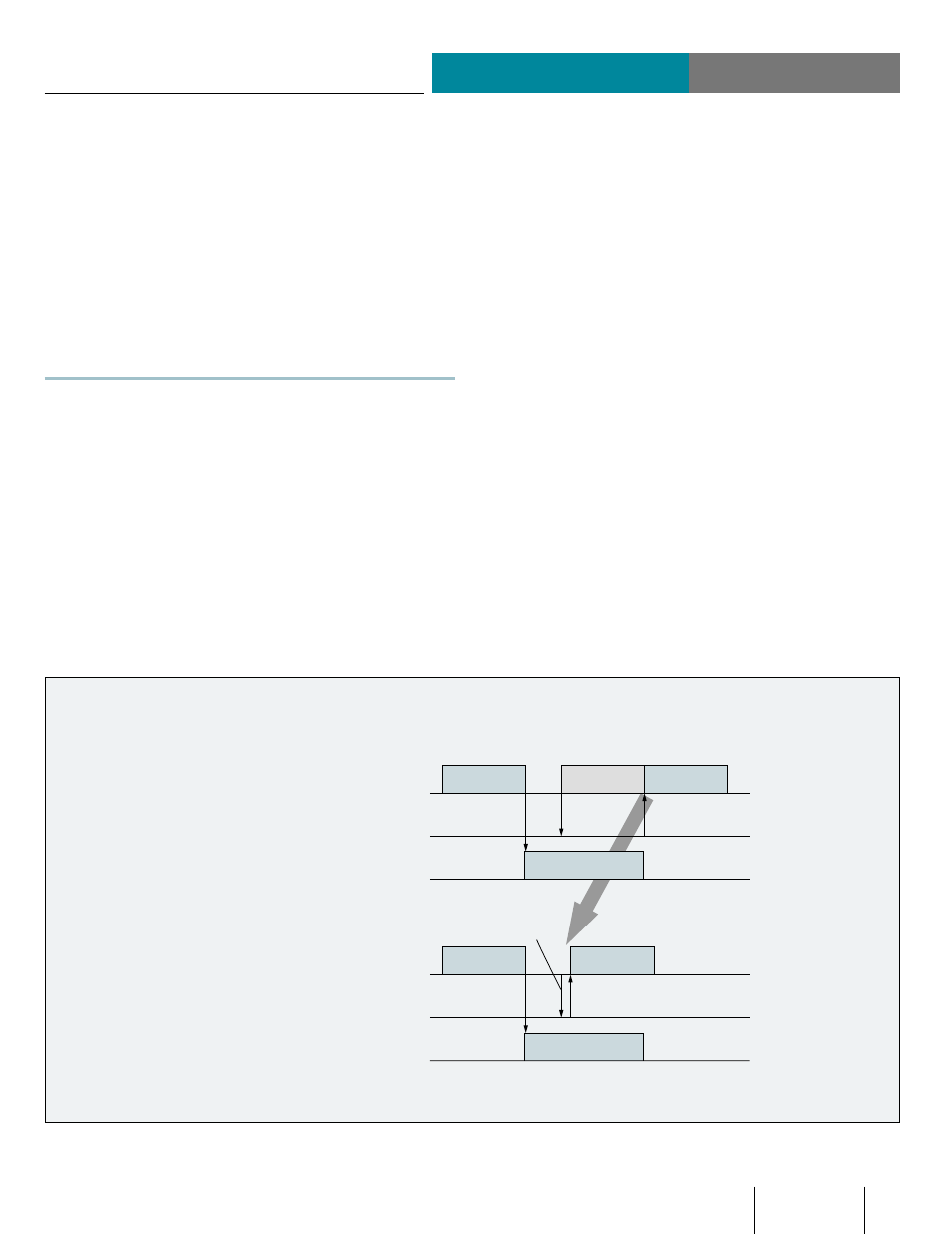

F i g . 1

outlines the operation of MB90F897 series

microcontrollers mounted with dual-operation flash

memories. While the upper bank flash memory handles

the execution of programs, the lower bank flash memory

can be applied for write/erase operations (or vice versa).

The new series also offers the following advantages for

system control.

■

No need to download programs to RAM when flash

memories self-rewrite to the CPU

Fig. 2

shows the operational flow for rewriting from flash

memories to the CPU.

In conventional microcontrollers mounted with flash

memories, programs have to be downloaded to RAM in

order to initiate rewrites, as these devices disallow rewrite

operations while programs are executed in the flash

memories. FUJITSU s new microcontrollers integrated

with dual-operation flash memory allow rewrites by

executing programs on flash memory, thereby eliminating

the need to transfer the programs to RAM. This obviates the

need to make provisions against power failures during

program execution on RAM, and cuts down the program

download time as well.

■

Flash memory rewrites performed concurrently with

system control

Fig. 3

illustrates the control sequence for rewriting the

flash memory using interruption.

Conventionally, FUJITSU s flash memory-integrated

microcontrollers have not been designed to allow

interruptions while the RAM is executing a program. After

the write/erase commands are issued, the software has to

check the flag to identify whether or not the write/erase

operation is completed. With the dual-operation flash

Figure 3 Control of Flash Memory Rewrite Based on Interruption