4 register descriptions, 1 reset and update register – 0x0, Register descriptions – Sundance SMT399-160 User Manual

Page 16: Reset and update register – 0x0, Figure 9 – register memory map

Word 1.

0x34

DDS1 – Register E (0xE) – RAM Segment Control

Word 1.

Read-back (FPGA Register) DDS1 – Register E (0xE).

0x35

DDS1 – Register F (0xF) – RAM Segment Control

Word 1.

Read-back (FPGA Register) DDS1 – Register F (0xF).

0x36

DDS1 – Register 10 (0x10) – RAM Segment Control

Word 2.

Read-back (FPGA Register) DDS1 – Register 10 (0x10).

0x37

DDS1 – Register 11 (0x11) – RAM Segment Control

Word 2.

Read-back (FPGA Register) DDS1 – Register 11 (0x11).

0x38

DDS1 – Register 12 (0x12) – RAM Segment Control

Word 2.

Read-back (FPGA Register) DDS1 – Register 12 (0x12).

0x39

DDS1 – Register 13 (0x13) – RAM Segment Control

Word 3.

Read-back (FPGA Register) DDS1 – Register 13 (0x13).

0x3A

DDS1 – Register 14 (0x14) – RAM Segment Control

Word 3.

Read-back (FPGA Register) DDS1 – Register 14 (0x14).

0x3B

DDS1 – Register 15 (0x15) – RAM Segment Control

Word 3.

Read-back (FPGA Register) DDS1 – Register 15 (0x15).

0x3C

DDS1 – Register 16 (0x1C) – Falling Delta Frequency

Tuning Word.

Read-back (FPGA Register) DDS1 - Falling Delta

Frequency Tuning Word.

0x3D

DDS1 – Register 17 (0x1D) – Falling Delta Frequency

Tuning Word.

Read-back (FPGA Register) DDS1 - Falling Delta

Frequency Tuning Word.

0x3E

DDS1 – Register 18 (0x1E) – Falling Sweep Ramp rate

Word.

Read-back (FPGA Register) DDS1 - Falling Sweep

Ramp rate Word.

0x3F

DDS1 – Register 19 (0x1F) – Rising Delta Frequency

Tuning Word.

Read-back (FPGA Register) DDS1 - Rising Delta

Frequency Tuning Word.

0x40

DDS1 – Register 20 (0x20) – Rising Delta Frequency

Tuning Word.

Read-back (FPGA Register) DDS1 - Rising Delta

Frequency Tuning Word.

0x41

DDS1 – Register 21 (0x21) – Rising Sweep Ramp rate

Word.

Read-back (FPGA Register) DDS1 - Rising Sweep

Ramp rate Word.

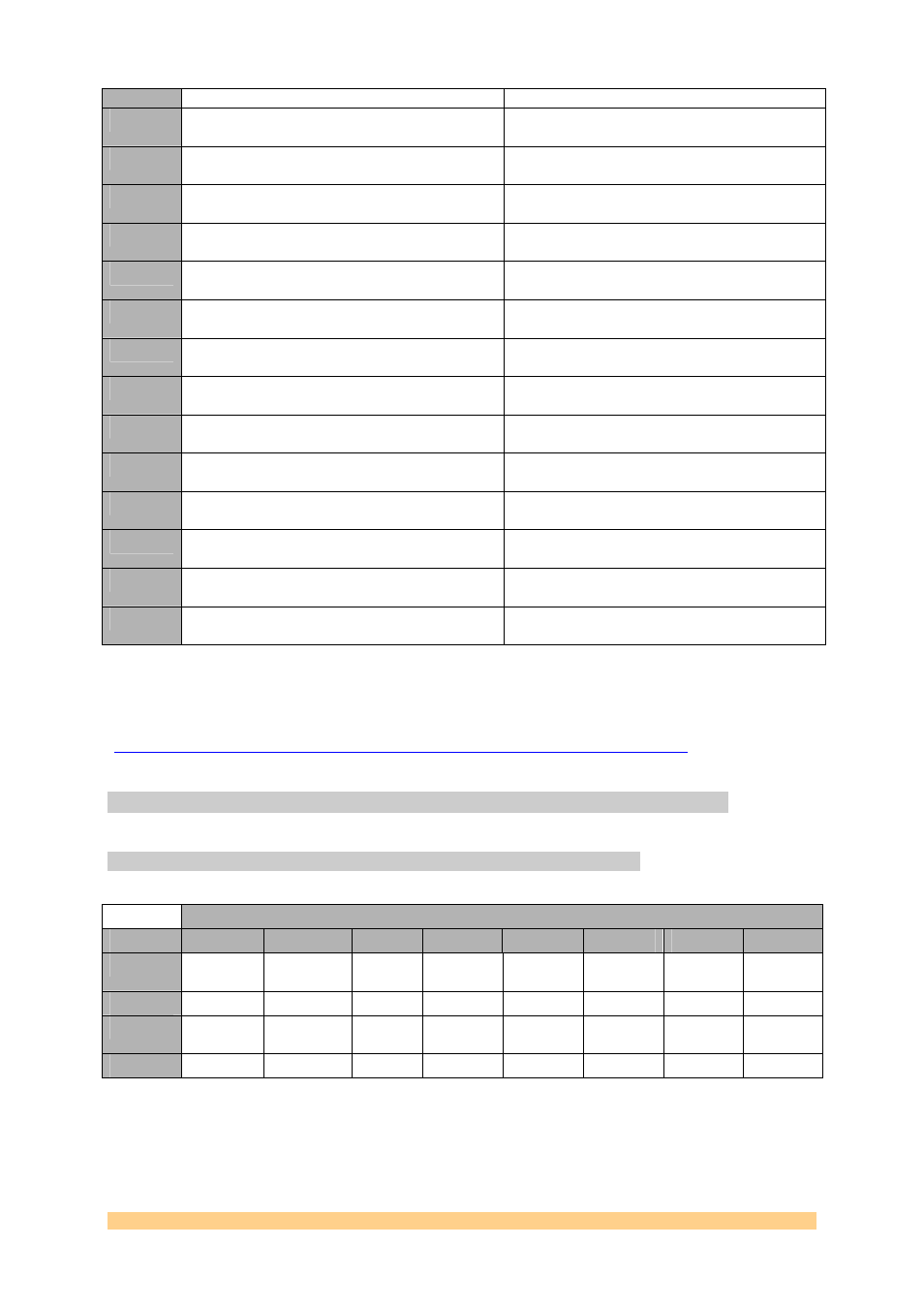

Figure 9 – Register Memory Map.

Analog Devices provides an Interactive Web Tool to calculate Tuning words. It can be found

at the following URL:

5.4 Register Descriptions

5.4.1 Reset and Update Register – 0x0.

Reset Register – 0x0

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

DDS1

IO_Update

DDS0

IO_Update

DDS1

Update

DDS0

Update

VGA3

Update

VGA2

Update

VGA1

Update

VGA0

Update

Default

‘0’ ‘0’ ‘0’

‘0’ ‘0’ ‘0’ ‘0’ ‘0’

0

Reserved Reserved DDS1

Reset

DDS0

Reset

VGA3

Reset

VGA2

Reset

VGA1

Reset

VGA0

Reset

Default

‘0’ ‘0’ ‘1’

‘1’ ‘1’ ‘1’ ‘1’ ‘1’

User Manual SMT399-160

Page 16 of 39

Last Edited: 24/05/2007 17:12:00