Upa data bus spice model, Advanced version, Sun microsystems, inc – Sun Microsystems SME5224AUPA-400 User Manual

Page 41: Worst case: z, 60 ω , t, 50 ω , t

13

400 MHz CPU, 4.0 MB E-Cache

UltraSPARC

™

-II CPU Module

SME5224AUPA-400

Advanced Version

July 1999

Sun Microsystems, Inc

UPA Data Bus SPICE Model

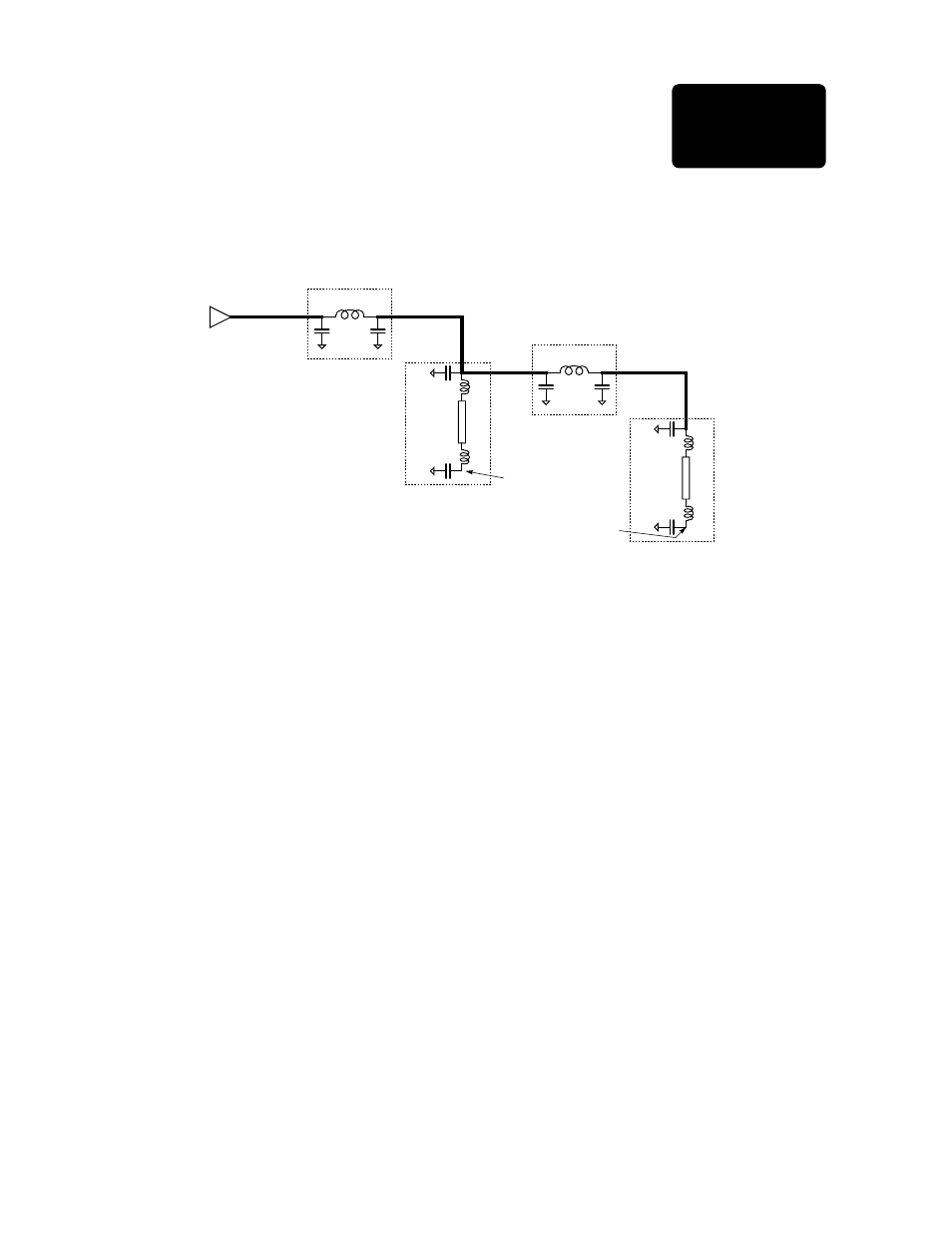

A typical circuit for the UPA data bus and ECC signals is illustrated in Figure 4:.

Figure 4. Module System Loading: Example for UPA_DATA, UPA_ECC

3.1 nH

1.0 pF

Edge Connector

UDB-II Driver

Trace 1

0.5 nH

2 nH

50

Ω

via 0.6 pF

7 pF

Trace 2

XB1 BGA Package Loading

3.1 nH

Edge Connector

Trace 3

0.5 nH

2 nH

50

Ω

via 0.6 pF

7 pF

UDB-II of Second Module

Package Loading

Trace 4

Measure point for XB1

Measure point for CPU

Worst Case: Z

0

= 60

Ω

, T

P

= 180 ps/inch, Trace 1 Length = 4.4”, Trace 2 Length = 0.6”, Trace 3 Length

= 1.2”, Trace 4 Length = 4.4”

Best Case: Z

0

= 50

Ω

, T

P

= 160 ps/inch, Trace 1 Length = 2.2”, Trace 2 Length = 0.2”, Trace 3 Length

= 0.2”, Trace 4 Length = 2.2”

1.0 pF

1.0 pF 1.0 pF