Pci bus latency, Pci bus latency -8, Table 3-3. pci originated latency matrix – Motorola MVME2400 User Manual

Page 56

3-8

Computer Group Literature Center Web Site

Functional Description

3

PCI Bus Latency

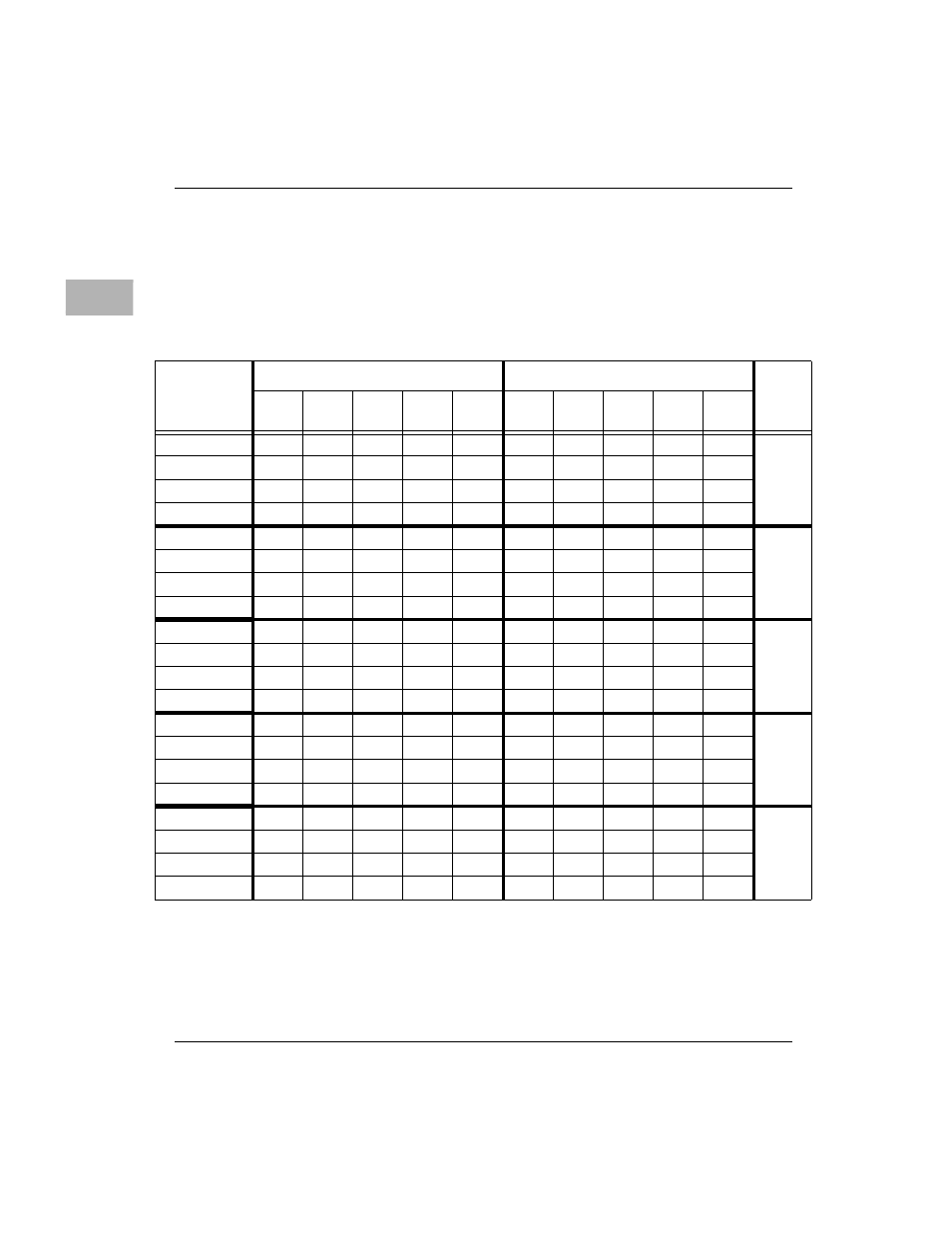

The following table lists the latency of PCI originated transactions for five

different clock ratios: 5:2, 3:2, 3:1, 2:1, and 1:1. The MVME2400 uses a

3:1 clock ratio:

Table 3-3. PCI Originated Latency Matrix

Transaction

32-bit PCI

64-bit PCI

Clock

Ratio

Beat

1

Beat

2

Beat

3

Beat

4

Total

Beat

1

Beat

2

Beat

3

Beat

4

Total

Burst Read

9

1

1

1

12

9

1

1

1

12

5:2

Burst Write

3

1

1

1

6

3

1

1

1

6

Single Read

9

-

-

-

9

9

-

-

-

9

Single Write

3

-

-

-

3

3

-

-

-

3

Burst Read

12

1

1

1

15

12

1

1

1

15

3:2

Burst Write

3

1

1

1

6

3

1

1

1

6

Single Read

12

-

-

-

12

12

-

-

-

12

Single Write

3

-

-

-

3

3

-

-

-

3

Burst Read

9

1

1

1

12

9

1

1

1

12

3:1

Burst Write

3

1

1

1

6

3

1

1

1

6

Single Read

9

-

-

-

9

-

-

-

-

-

Single Write

3

-

-

-

3

-

-

-

-

-

Burst Read

11

1

1

1

14

11

1

1

1

14

2:1

Burst Write

3

1

1

1

6

3

1

1

1

6

Single Read

11

-

-

-

11

-

-

-

-

-

Single Write

3

-

-

-

3

-

-

-

-

-

Burst Read

16

1

1

1

19

16

1

1

1

19

1:1

Burst Write

3

1

1

1

6

3

1

1

1

6

Single Read

16

-

-

-

16

-

-

-

-

-

Single Write

3

-

-

-

3

-

-

-

-

-