Tim sites, Jtag, Cpu & i/o – Sundance SMT118LT User Manual

Page 6: Comm-ports

Version 1.0

Page 6 of 10

SMT118v2 User Manual

TIM sites

The SMT118LT has three TIM sites. None of the TIM sites include the global bus

connector.

JTAG

The JTAG chain includes all three TIM sites with the proviso that there must always

be a CPU module in SITE 1, or a module that connects TDI to TDO.

A standard 14-pin XDS510 compatible header (CONN9) is provided to allow

debugging.

In addition to the TI standard 14-pin JTAG header, there is a 20 way 0.050” pitch

high-density connector which allows direct JTAG conne

PCI TIM motherboards with embedded test bus controller.

CPU & I/O

There is no differentiation between the CPU and I/O TIM sites other than the JTAG

requirement mentioned above.

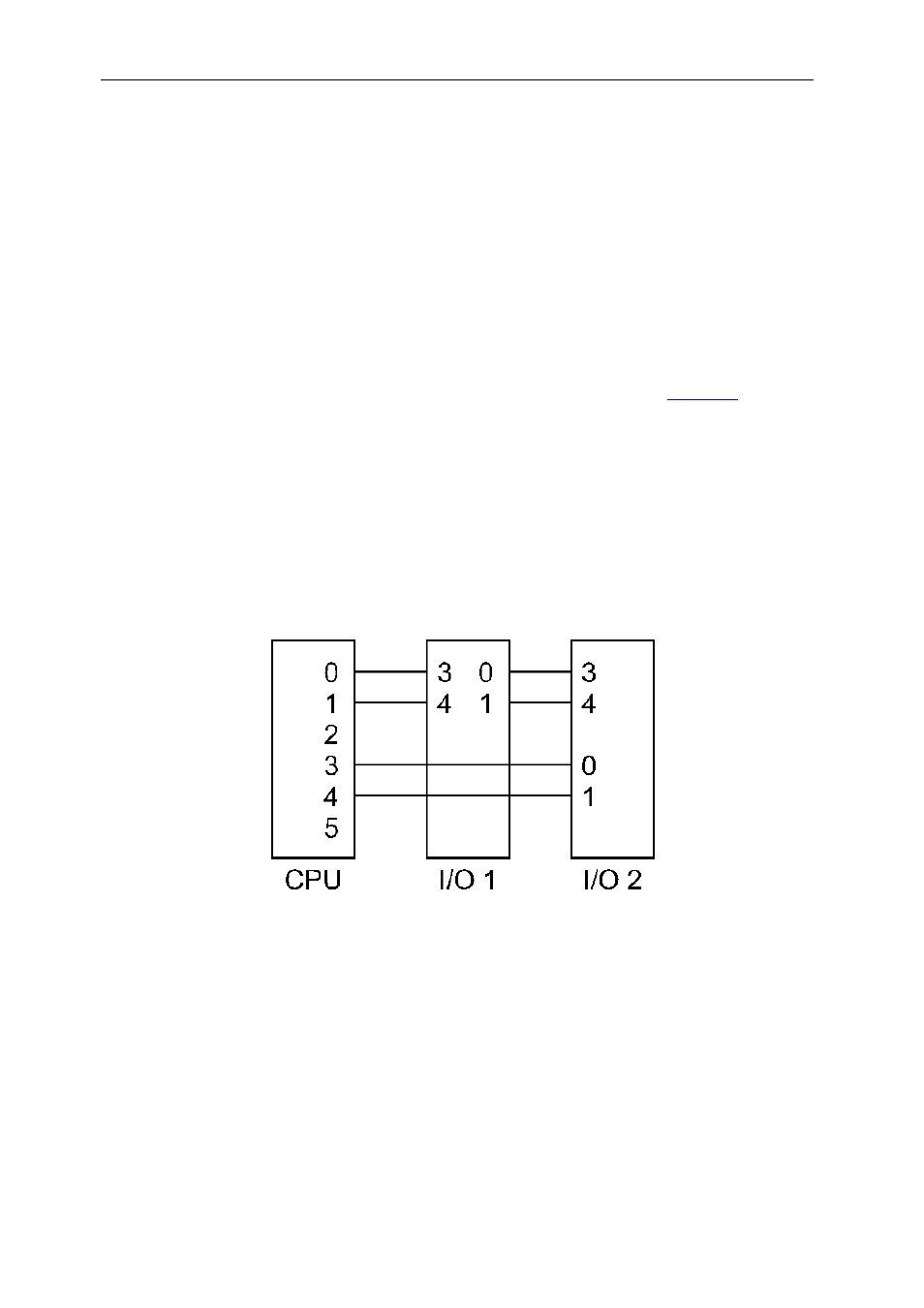

Comm-ports

Full Comm-port connectivity is provided using the following scheme:

With this method, a dual pipe exists between the modules in a 0-3 and 1-4 routing

fashion. Taking the global bus issues into consideration, three CPU TIMs could be

mounted on the SMT118LT and good Comm-port communications established.

No active or passive electronic circuitry is connected to these Comm-ports but in

normal operating conditions no signal is left un-driven for any length of time.