Resources usage and performances, Testbench and matlab programs – Sundance FC108 v.1.1 User Manual

Page 6

FC108 - Polyphase filterbank

v1.1

Fast

Polyphase filterbank product manual

December 2005

www.sundance.com

- 6 -

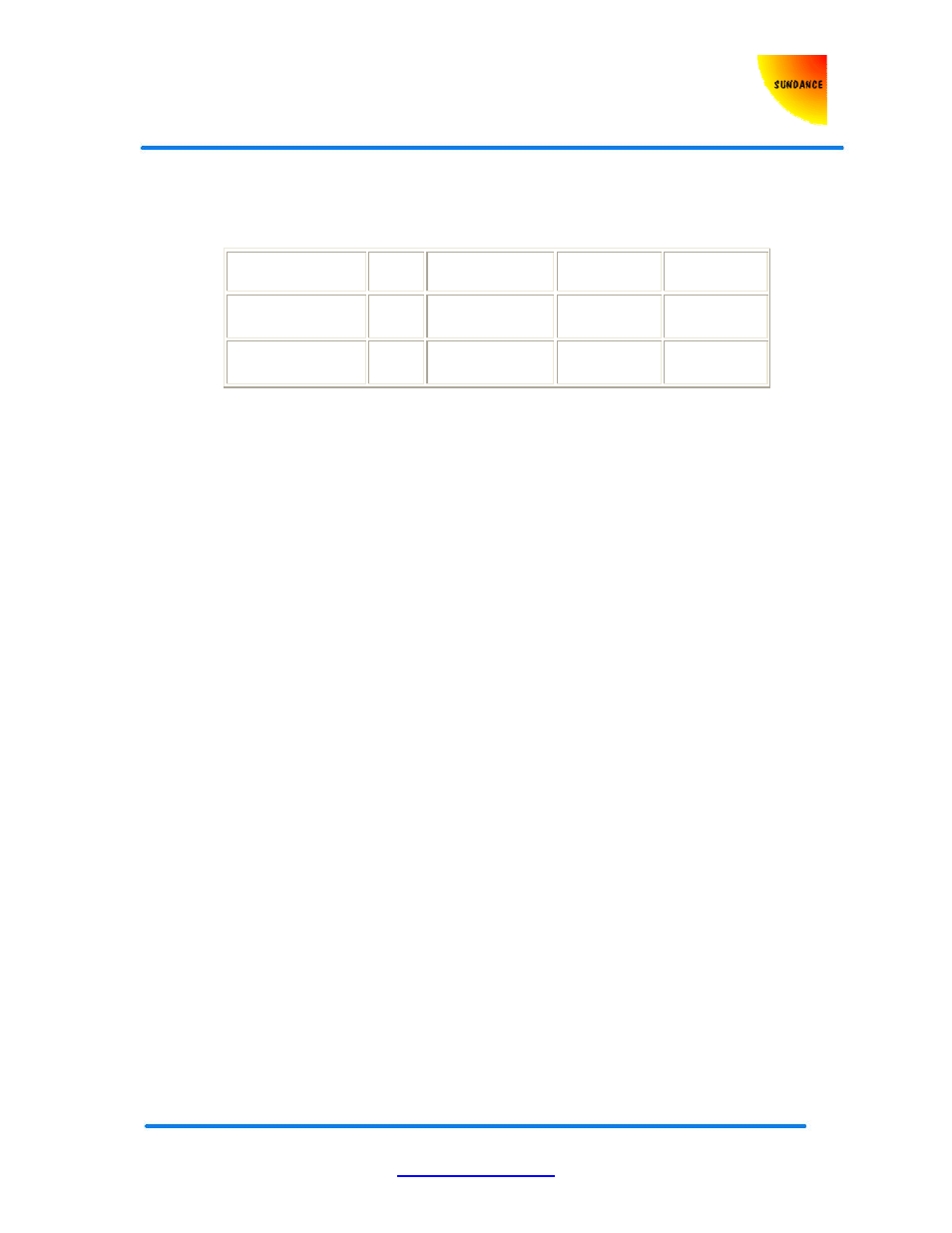

Resources usage and performances

Device Slices

Multipliers

18x18

Block RAMs

18Kb

Fmax

Virtex-II Pro

XC2VP40 -7

5,901

36 157

125.0MHz

Virtex-II

XC2V8000

5,230

36 157

106.7

MHz

Table2 : Resources usage and performances

Testbench and Matlab programs

The Filterbank core package comprises a VHDL testbench and two Matlab programs to

generate data and check results.

Filterbank_TB.vhd

: This testbench is designed to work with the Filterbank core. It extracts

the core parameters from the ‘settings.txt’ file and load the filter taps from the ‘filter_taps.txt’

file. The input data are also read from a file (‘data_in.txt’) and continuously sent to the core

once started. Upon the simulation completion, the results are written to the ‘data_out.txt’ file.

Please make sure that the file paths in the testbench VHDL file are pointing to the folder where

the files are being stored.

filterbank_in.m

: This Matlab program generates the parameters, filter taps and data in format

expected by the core (see Data format). The filterbank core data and the filter taps are saved in

an ASCII format respectively in the ‘data_in.txt’ and ‘filter_taps.txt’ files. A third file,

‘settings.txt’, contains the parameters for thefilterbank core simulation.

Please make sure that the file paths in the FFT_test.m Matlab program are pointing to the same

files as the VHDL testbench.

filterbank_out.m

: This Matlab program reads the files generated by the filterbank_in.m

program as well the results of the simulation from the ‘data_out.txt’ file. It then performs the

data processing as per Equation 4 and calculates for each data batch the Signal To Noise Ratio

(SNR) that is written to the ‘SNR.txt’ file.

Please make sure that the file paths in the FFT_test.m Matlab program are pointing to the same

files as the VHDL testbench.