6 Page 19

Page 19

P4LA User’s Manual Hardware Setup

Enhanced IDE Interface

19

2.6

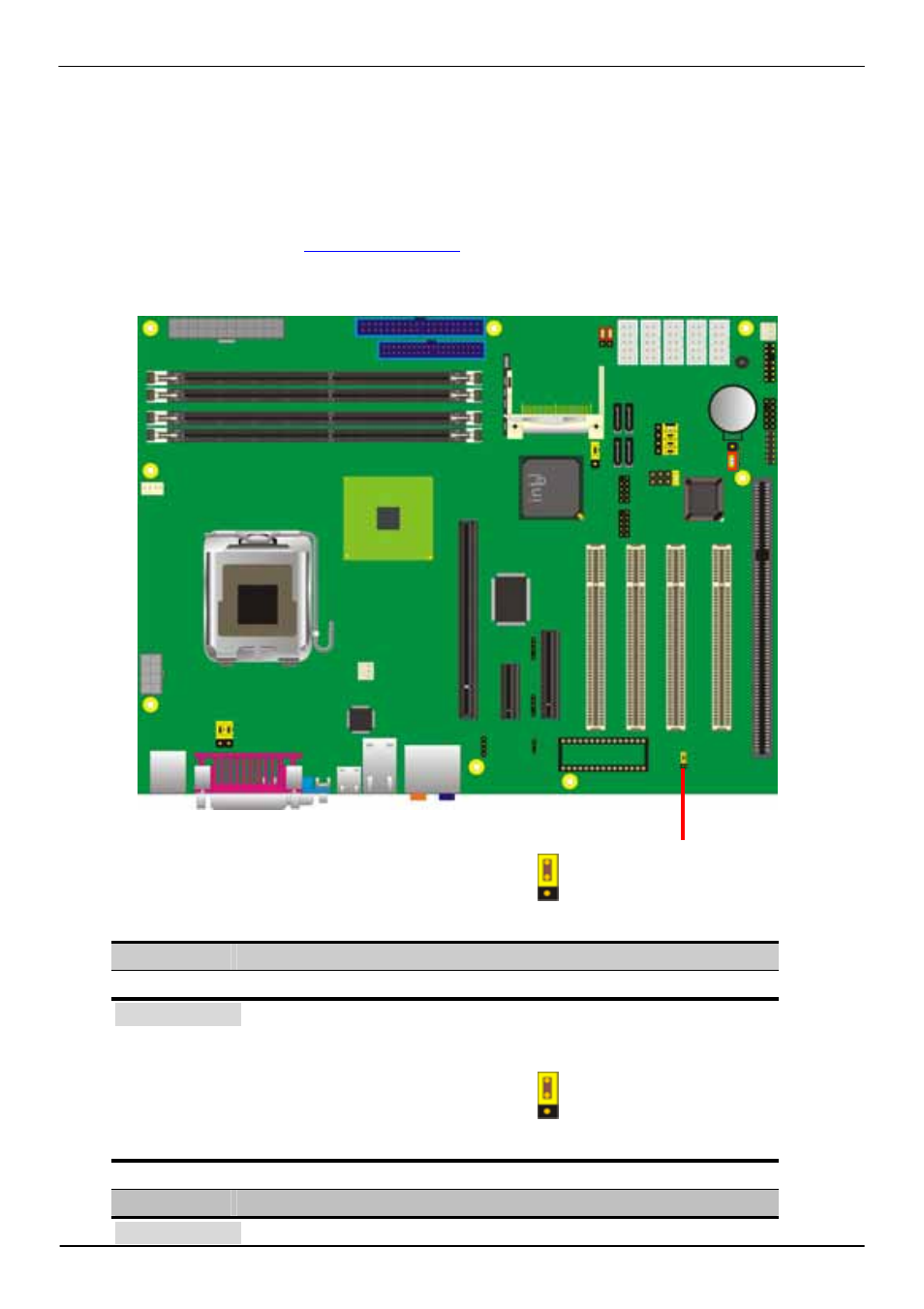

The Intel® ICH7R (south bridge chip) supports one enhanced IDE interface, dual channel

for two ATAPI devices with ATA100. Based on this function, P4LA has one 40-pin IDE

connector with jumper selectable for pin-20 +5V supported.

The board supports 32-pin

DiskOnChip 2000

. The onboard 32-pin socket, DOC, supports

DiskOnChip2000 single chip flash disk in 32-pin DIP JEDEC with jumper selectable address

on jumper JDOC.

Jumper: JDOC

Type: onboard 3-pin header

JDOC DiskOnChip

Address

1-2

D800h

2-3

D000h

Default setting

Jumper: JCFSEL

Type: onboard 3-pin header

JCFSEL

Compact Flash Address Setting

1-2 Master

2-3

Slave

Default setting

IDE1

JDOC

1

3

DOC

JCFSEL

3

1

JDOC

- FS-A76 (41 pages)

- LV-67H (62 pages)

- FS-A78 (50 pages)

- FS-A73 (52 pages)

- FS-A74 (45 pages)

- FS-A72 (54 pages)

- FS-A71 (49 pages)

- FE-97G (55 pages)

- FS-97E (54 pages)

- FS-A70 (53 pages)

- FS-97B (58 pages)

- FS-97D (61 pages)

- FS-97C (55 pages)

- HS-870S (53 pages)

- FS-977 (42 pages)

- FS-961 (46 pages)

- HE-875P (56 pages)

- HS-874P (58 pages)

- HS-873P (52 pages)

- HS-872PE (56 pages)

- HS-862P (46 pages)

- HE-860S (37 pages)

- HE-B71 (46 pages)

- HS-B70 (51 pages)

- HS-773 (56 pages)

- HE-772 (53 pages)

- HS-770E (46 pages)

- HE-760 (41 pages)

- HS-771 (48 pages)

- LE-575 (61 pages)

- LS-573 (54 pages)

- LS-572 (64 pages)

- LS-571 (57 pages)

- LE-37E (29 pages)

- LS-570E (58 pages)

- LE-565 (55 pages)

- LE-37D (39 pages)

- LS-37B (49 pages)

- LE-37C (47 pages)

- LE-380 (51 pages)

- LE-379 (53 pages)

- LS-377 (47 pages)

- LE-376 (45 pages)

- LE-375 (45 pages)

- LE-374 (54 pages)