Figure 7-11, Figure 7-10 – Elenco MicroMaster ® Computer Training Kit User Manual

Page 42

7-7

T

1

T

2

T

WAIT

T

3

T

4

T

5

T

6

T

RESET

T

HALT

T

HOLD

X

X

X

X

1

1

1

X

0

X

X

X

X

X

0*

0*

0*

TS

TS

TS

X

X

X

X

X

X

X

TS

TS

TS

X

X

X

X

TS

TS

TS

TS

TS

TS

1

X

X

X

1

1

1

TS

TS

TS

1

X

X

X

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

Status & Buses

Control

S1,S0 IO/M A

8

-A

15

AD

0

-AD

7

RD,WR INTA ALE

Machine

State

0=Logic “0” 1=Logic “1” TS=High Impedance X=Unspecified

ALE not generated during 2nd and 3rd machine cycles of

DAD instruction.

* IO/M = 1 during T

4

- T

6

states of RST and INA cycles.

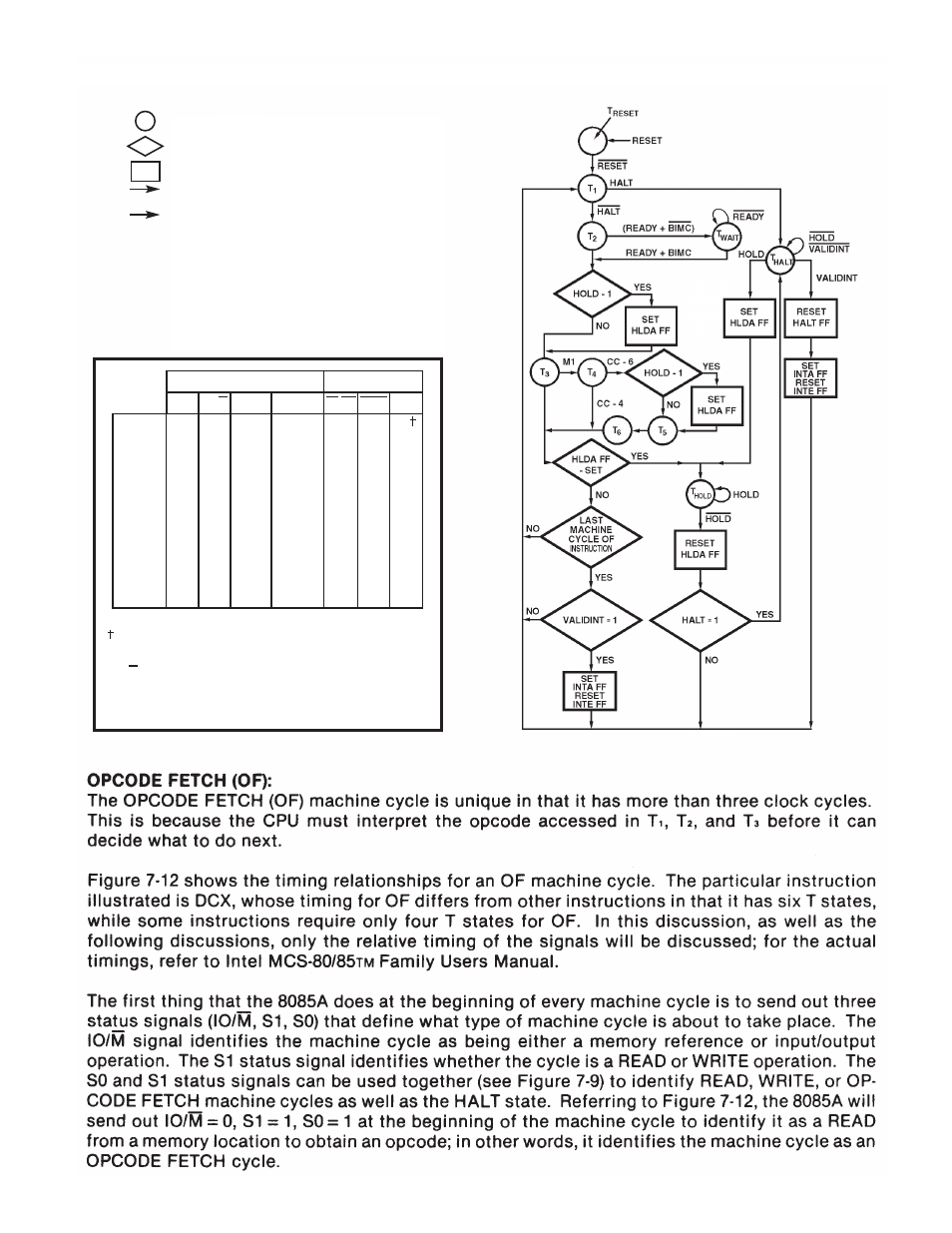

Figure 7-11

8085A MACHINE STATE CHART

Figure 7-10

8085A CPU STATE TRANSISTION

= CPU STATE Tx ALL CPU STATE TRANSISTIONS OCCUR ON

THE FALLING EDGE OF CLK

= A DECISION (X) THAT DETERMINES WHICH SEVERAL

ALTERNATIVE PATHS TO FOLLOW.

= PERFORM THE ACTION X.

= FLOWLINE THAT INDICATES THE SEQUENCE OF EVENTS.

= FLOWLINE THAT INDICATES THE SEQUENCE OF EVENTS

IF CONDITION X IS TRUE.

= NUMBER OF CLOCK CYCLES IN THE CURRENT MACHINE

CYCLE.

= “BUS IDLE MACHINE CYCLE” = MACHINE CYCLE WHICH

DOESN’T USE THE SYSTEM BUS.

= “VALID INTERRUPT” - AN INTERRUPT IS PENDING THAT IS

BOTH ENABLED AND UNMASKED (MASKING ONLY

APPLIES FOR RST 5.5, 6.5, AND 7.5 INPUTS).

= INTERNAL HOLD ACKNOWLEDGE FLIP FLOP. NOTE THAT

THE 8085A SYSTEM BUSES ARE 3-STATED ONE CLOCK

CYCLE AFTER THE HLDA FLIP FLOP IS SET.

T

X

X

X

CC

X

BIMC

VALIDINT

HLDA FF

NOTE: SYMBOL DEFINITION