3 chipset chipset chipset chipset chipset, Chip-kill mode enable [disabled, Ecc redirection [disabled – Asus K8N-DL User Manual

Page 85: Dram background scrubber [disabled, L2 cache background scrubber [disabled, Dcache background scrubber [disabled

A S U S K 8 N - D L

A S U S K 8 N - D L

A S U S K 8 N - D L

A S U S K 8 N - D L

A S U S K 8 N - D L

4 - 2 3

4 - 2 3

4 - 2 3

4 - 2 3

4 - 2 3

Chip-Kill Mode Enable [Disabled]

Chip-Kill Mode Enable [Disabled]

Chip-Kill Mode Enable [Disabled]

Chip-Kill Mode Enable [Disabled]

Chip-Kill Mode Enable [Disabled]

When set to [Enabled], allows ECC checking to be based on a 128/16

data/ECC rather than on a 64/8 data/ECC. You may only enable this

feature in 128-bit DRAM data width mode. Configuration options:

[Disabled] [Enabled]

ECC Redirection [Disabled]

ECC Redirection [Disabled]

ECC Redirection [Disabled]

ECC Redirection [Disabled]

ECC Redirection [Disabled]

When set to [Enabled], correctable errors are corrected as the data is

passed to the requestor. The data in the DRAM is not corrected if this item

is set to [Disabled]. Configuration options: [Disabled] [Enabled]

DRAM Background Scrubber [Disabled]

DRAM Background Scrubber [Disabled]

DRAM Background Scrubber [Disabled]

DRAM Background Scrubber [Disabled]

DRAM Background Scrubber [Disabled]

Specifies the scrub rate of the next address to be scrubbed by the DRAM

scrubber. Configuration options: [Disabled] [40.0ns]

L2 Cache Background Scrubber [Disabled]

L2 Cache Background Scrubber [Disabled]

L2 Cache Background Scrubber [Disabled]

L2 Cache Background Scrubber [Disabled]

L2 Cache Background Scrubber [Disabled]

Specifies the scrub rate of the next address to be scrubbed by the L2

cache scrubber. Configuration options: [Disabled] [40.0ns]

DCache Background Scrubber [Disabled]

DCache Background Scrubber [Disabled]

DCache Background Scrubber [Disabled]

DCache Background Scrubber [Disabled]

DCache Background Scrubber [Disabled]

Specifies the scrub rate of the next address to be scrubbed by the data

cache scrubber. Configuration options: [Disabled] [40.0ns]

4.4.3

4.4.3

4.4.3

4.4.3

4.4.3

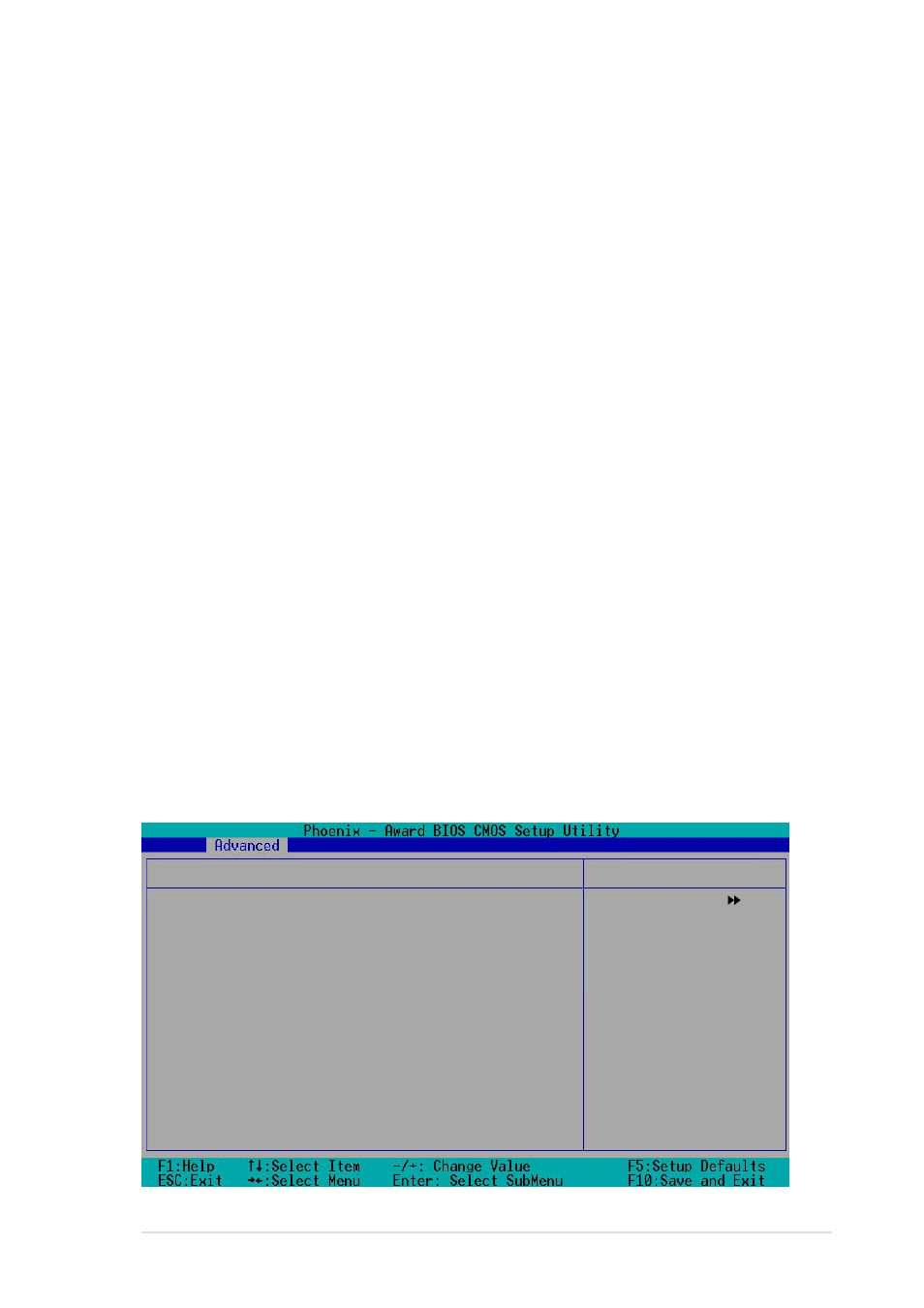

Chipset

Chipset

Chipset

Chipset

Chipset

This menu shows the chipset configuration settings. Select an item then

press

Select Menu

Item Specific Help

Disable/Enable OnChip IDE

Channel0.

Chipset

OnChip IDE Channel0

[Enabled]

OnChip IDE Channel1

[Enabled]

Hyper Transport Frequency

[4x]

Hyper Transport Width

[

↓↓↓↓↓

16

↑↑↑↑↑

16]

Errata 94 Enhanced

[Auto]

System BIOS Cacheable

[Disabled]

Spread Spectrum

[Enabled]

SATA Spread Spectrum

[Disabled]

PCIE Spread Spectrum

[Disabled]

SSE/SSE2 Instructions

[Enabled]

Init Display First

[PCI Slot]

IDE DMA Transfer Access

[Enabled]

Serial-ATA 1

[Enabled]

SATA DMA Transfer

[Enabled]

Serial-ATA 2

[Enabled]

SATA2 DMA Transfer

[Enabled]

IDE Prefetch Mode

[Enabled]