Asus P5GV-MX User Manual

Page 70

2-24

Chapter 2: BIOS setup

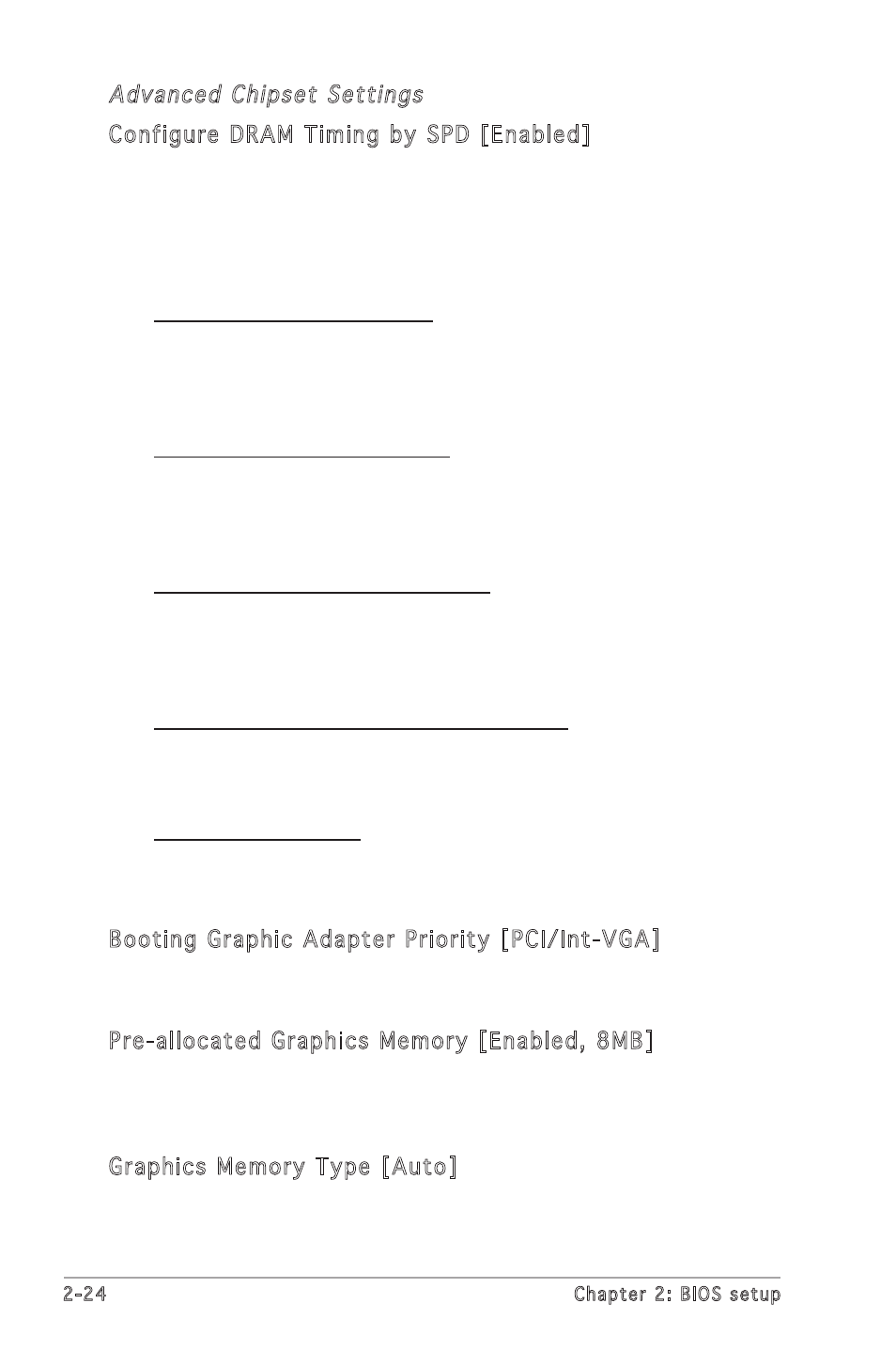

Advanced Chipset Settings

Configure DRAM Timing by SPD [Enabled]

When this item is enabled, the DRAM timing parameters are set according

to the DRAM SPD (Serial Presence Detect). When disabled, you can

manually set the DRAM timing parameters through the DRAM sub-items.

The following sub-items appear when this item is Disabled.

Configuration options: [Disabled] [Enabled]

DRAM CAS# Latency [3 Clocks]

Controls the latency between the SDRAM read command and the time

the data actually becomes available.

Configuration options: [3 Clocks] [2.5 Clocks] [2 Clocks]

DRAM RAS# Precharge [4 Clocks]

Controls the idle clocks after issuing a precharge command to the DDR

SDRAM. Configuration options: [2 Clocks] [3 Clocks] [4 Clocks]

[5 Clocks]

DRAM RAS# to CAS# Delay [4 Clocks]

Controls the latency between the DDR SDRAM active command and

the read/write command. Configuration options: [2 Clocks] [3 Clocks]

[4 Clocks] [5 Clocks]

DRAM RAS# Activate to Precharge [15 Clocks]

Sets the RAS Activate timing to Precharge timing.

Configuration options: [1 Clocks] [2 Clocks] ~ [15 Clocks]

DRAM Burst Length [8]

Sets the DRAM Burst Length.

Configuration options: [4] [8]

Booting Graphic Adapter Priority [PCI/Int-VGA]

Allows selection of the graphics controller to use as primary boot device.

Configuration options: [Internal VGA] [PCI/Int-VGA]

Pre-allocated Graphics Memory [Enabled, 8MB]

Disables or sets the amount of system memory pre-allocated by the

internal graphics device. Configuration options: [Disabled] [Enabled, 1MB]

[Enabled, 8MB]

Graphics Memory Type [Auto]

Sets the graphics memory type.

Configuration options: [Auto] [DVMT] [FIX] [DVMT+FIX]