At89lv52, Shift register mode timing waveforms, Ac testing input/output waveforms – Rainbow Electronics АТ89LV52 User Manual

Page 20: Float waveforms

AT89LV52

4-102

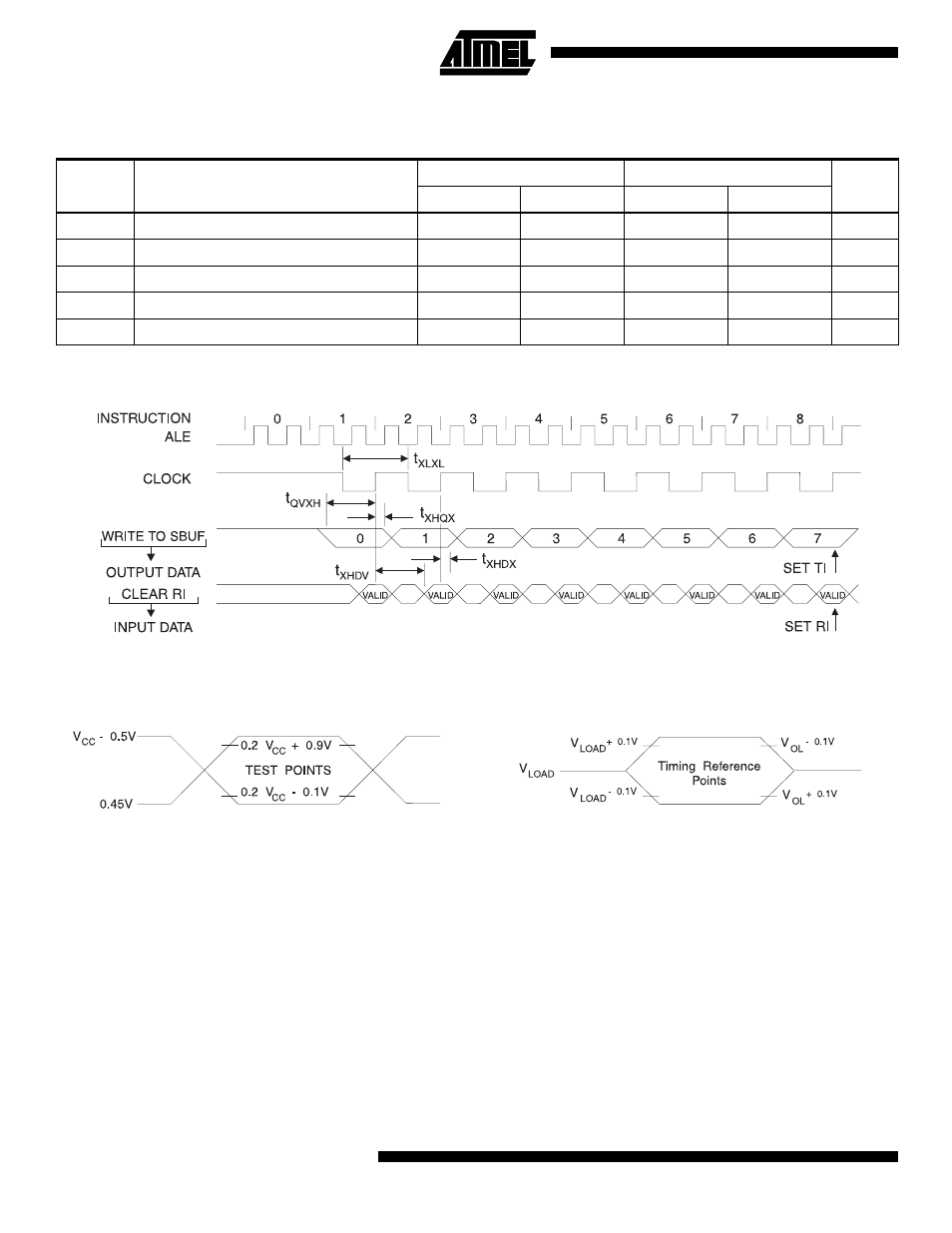

Serial Port Timing: Shift Register Mode Test Conditions

The values in this table are valid for V

CC

= 2.7V to 6.0V and Load Capacitance = 80 pF.

Shift Register Mode Timing Waveforms

Symbol

Parameter

12 MHz Osc

Variable Oscillator

Units

Min

Max

Min

Max

t

XLXL

Serial Port Clock Cycle Time

1.0

12t

CLCL

µ

s

t

QVXH

Output Data Setup to Clock Rising Edge

700

10t

CLCL

-133

ns

t

XHQX

Output Data Hold After Clock Rising Edge

50

2t

CLCL

-117

ns

t

XHDX

Input Data Hold After Clock Rising Edge

0

0

ns

t

XHDV

Clock Rising Edge to Input Data Valid

700

10t

CLCL

-133

ns

AC Testing Input/Output Waveforms

(1)

Note:

1.

AC Inputs during testing are driven at V

CC

- 0.5V for

a logic 1 and 0.45V for a logic 0. Timing measure-

ments are made at V

IH

min. for a logic 1 and V

IL

max. for a logic 0.

Float Waveforms

(1)

Note:

1.

For timing purposes, a port pin is no longer floating

when a 100 mV change from load voltage occurs. A

port pin begins to float when a 100 mV change from

the loaded V

OH

/V

OL

level occurs.