Ds8102 dual delta-sigma modulator and encoder, Configuration inputs, Table 1. modulator 0 gain settings – Rainbow Electronics DS8102 User Manual

Page 6

DS8102

Dual Delta-Sigma Modulator and Encoder

6

_______________________________________________________________________________________

Once the power supply is at an acceptable level

(V

DD

> V

RST

) and the RST line is driven high, the

DS8102 exits shutdown mode. However, a warmup

sequence must then be completed before analog-to-

digital conversion and Manchester encoding begins.

The length of this sequence depends on the

internal/external voltage reference mode (controlled by

the APDREF pin).

If the external voltage reference is selected (APDREF = 1),

the following actions are performed:

1) Upon exit from shutdown mode (V

DD

> V

RST

and

RST = 1), the 8MHz oscillator is started.

2) The DS8102 delays for 16 cycles of the 8MHz oscil-

lator. This allows the 8MHz oscillator to warm up.

3) The analog front-end (AFE) is enabled.

4) The DS8102 delays for 8192 cycles of the 8MHz

oscillator. This allows the AFE to warm up.

5) If CLKSEL = 1, the 8MHz oscillator is disabled at

this point and the DS8102 switches to the external

clock source provided at CLKIO.

6) Both modulator channels are enabled, and the

DS8102 begins performing conversions using the

external voltage reference.

If the internal voltage reference is selected (APDREF = 0),

the followings actions are performed:

1) Upon exit from shutdown mode (V

DD

> V

RST

and

RST = 1), the 8MHz oscillator is started.

2) The DS8102 delays for 16 cycles of the 8MHz oscil-

lator. This allows the 8MHz oscillator to warm up.

3) The AFE is enabled.

4) The DS8102 delays for 8192 cycles of the 8MHz

oscillator. This allows the AFE to warm up.

5) The internal voltage reference is enabled.

6) The DS8102 delays for an additional 57,344 cycles

of the 8MHz oscillator. This allows the internal refer-

ence to warm up.

7) If CLKSEL = 1, the 8MHz oscillator is disabled at

this point and the DS8102 switches to the external

clock source provided at CLKIO.

8) Both modulator channels are enabled, and the

DS8102 begins performing conversions using the

internal voltage reference.

Even if the external clock has been selected by setting

CLKSEL = 1, the internal 8MHz oscillator is still used to

control the warmup sequence. Once the warmup

sequence has completed, the internal 8MHz oscillator

is disabled if CLKSEL = 1.

Active Mode

In active mode, the AFE and delta-sigma modulators on

the DS8102 are enabled, and the DS8102 converts and

outputs samples over the Manchester-encoded output

(MNOUT) at a rate determined by either the internal

8MHz oscillator (if CLKSEL = 0) or the external clock

input at CLKIO (if CLKSEL = 1).

If RST is driven low or if V

DD

drops below the V

RST

level, the DS8102 enters shutdown mode immediately

and must go through the warmup sequence again

(once V

DD

> V

RST

and RST = 1) to return to active

mode.

Configuration Inputs

The input pins G0, G1, APDREF, and CLKSEL are con-

figuration inputs for the DS8102 that determine its oper-

ating mode, including:

• Clock selection—internal or external

• Voltage reference—internal or external

• Gain setting for analog input channel 0—1x, 4x, 16x,

or 32x

These pins must be set to a valid level for proper oper-

ation; they cannot be left disconnected. If any of the

configuration inputs are driven by a companion micro-

controller (as opposed to being statically connected to

V

DD

or GND), the inputs can only be changed when the

DS8102 is in shutdown mode.

Channel 0 Gain Selection

Configuration input pins G0 and G1 are used to select

the gain setting for analog input channel 0. The avail-

able gain configurations are 1x, 4x, 16x, and 32x. The

effective input voltage range scales downward propor-

tionally with each increased gain selection. For exam-

ple, full-scale output at gain = 1x occurs when AN0+ is

2V higher than AN0-. However, with the gain setting at

4x, the output reaches full scale when AN0+ is only

500mV higher than AN0-.

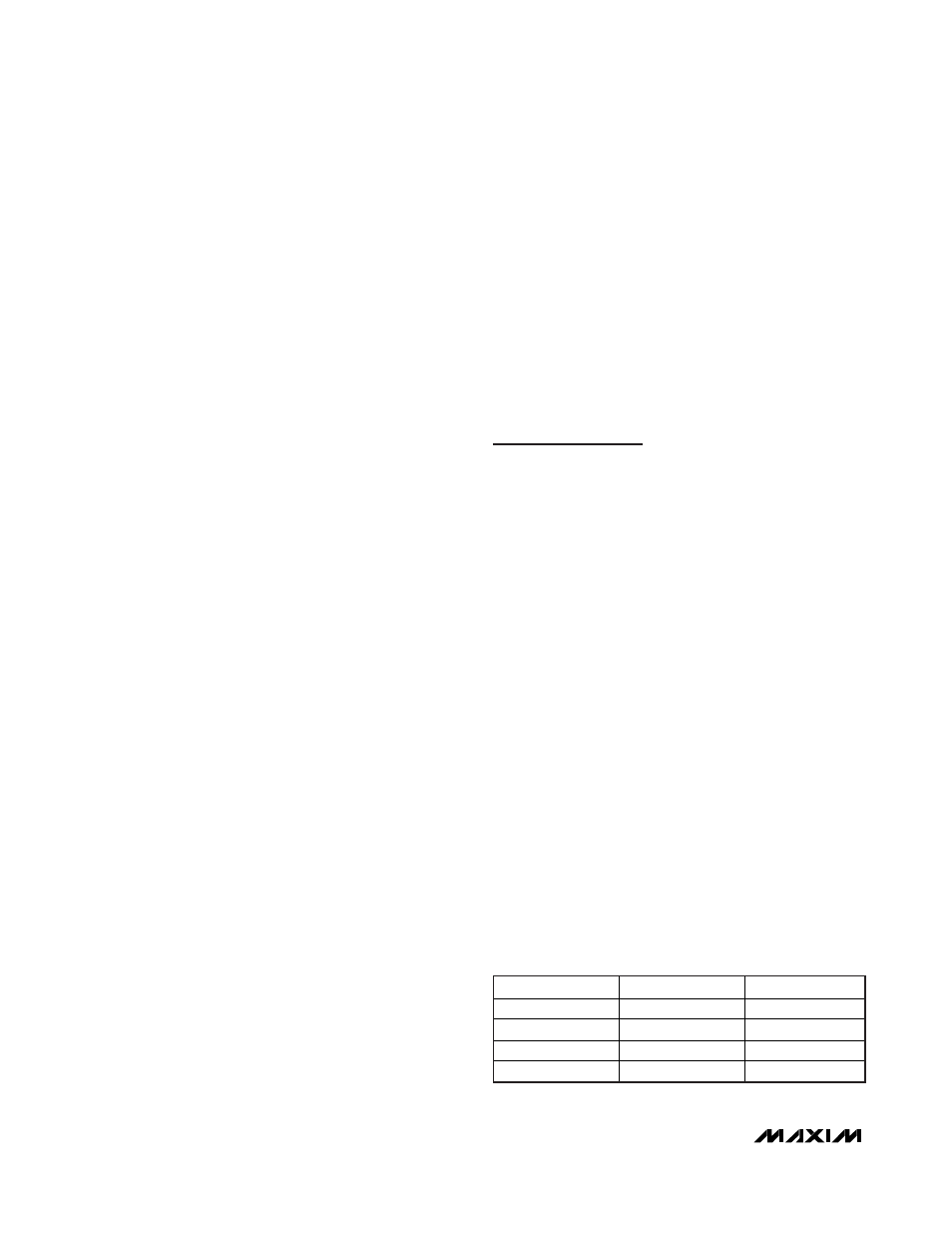

Table 1 lists the gain configuration settings available for

channel 0. The levels at G0 and G1 should be set when

the DS8102 is in shutdown mode.

G1 PIN

G0 PIN

GAIN

0 0 1x

0 1 4x

1 0

16x

1 1

32x

Table 1. Modulator 0 Gain Settings