W78c32c – Rainbow Electronics W78C32C User Manual

Page 8

W78C32C

- 8 -

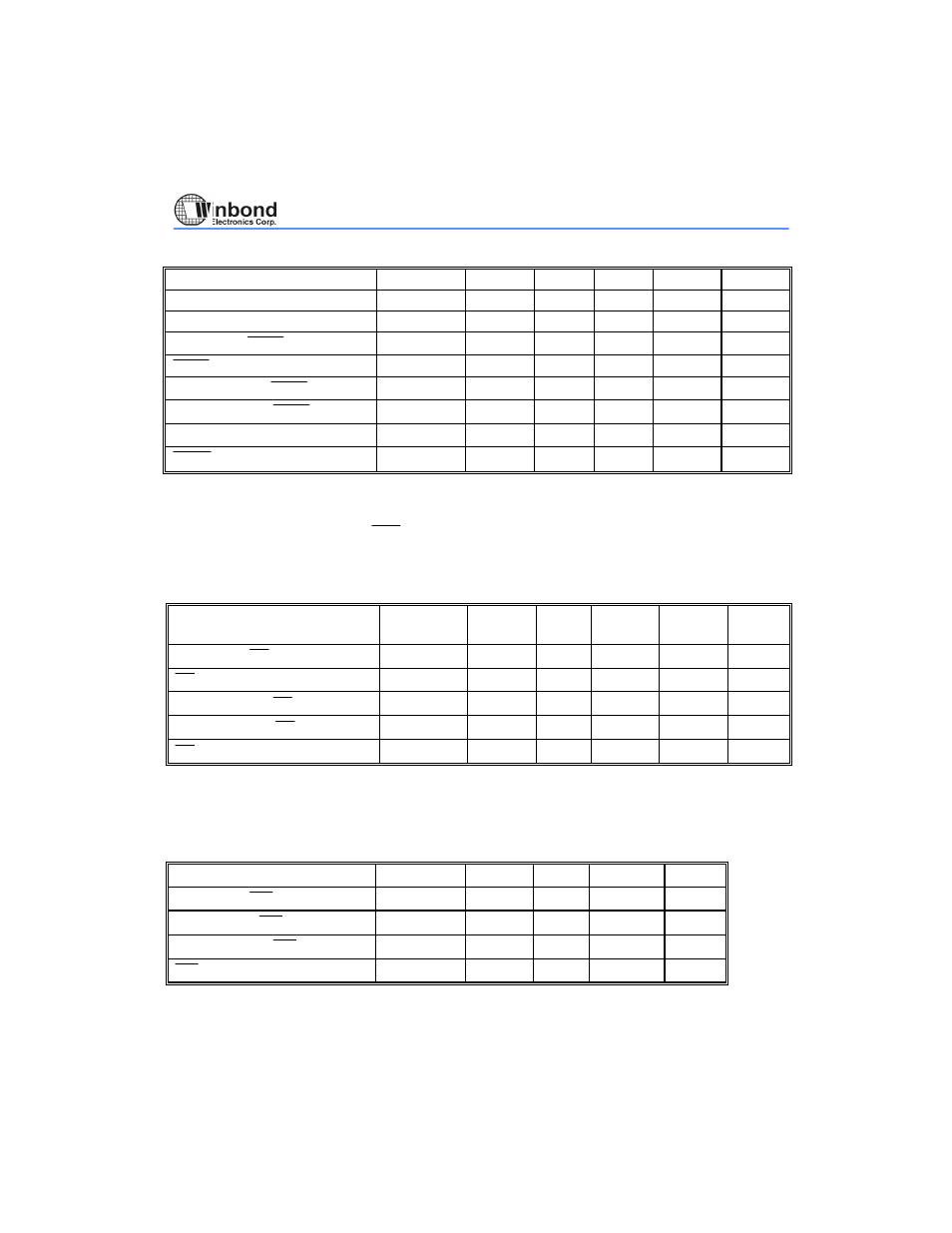

Program Fetch Cycle

PARAMETER SYMBOL

MIN.

TYP. MAX. UNIT NOTES

Address Valid to ALE Low

T

AAS

1 T

CP

-

∆

-

-

nS

4

Address Hold after ALE Low

T

AAH

1 T

CP

-

∆

- - nS 1,

4

ALE Low to PSEN Low

T

APL

1 T

CP

-

∆

- - nS 4

PSEN Low to Data Valid

T

PDA

- -

2

T

CP

nS

2

Data Hold after PSEN High

T

PDH

0 -

1

T

CP

nS

3

Data Float after PSEN High

T

PDZ

0

-

1

T

CP

nS

ALE Pulse Width

T

ALW

2 T

CP

-

∆ 2 T

CP

-

nS

4

PSEN

Pulse Width

T

PSW

3 T

CP

-

∆ 3 T

CP

-

nS

4

Notes:

1. P0.0

−P0.7, P2.0−P2.7 remain stable throughout entire memory cycle.

2. Memory access time is 3 T

CP

.

3. Data have been latched internally prior to PSEN going high.

4. "

∆" ( due to buffer driving delay and wire loading) is 20 nS.

Data Read Cycle

PARAMETER SYMBOL

MIN.

TYP.

MAX.

UNIT NOTE

S

ALE Low to RD Low

T

DAR

3 T

CP

-

∆

-

3 T

CP+

∆

nS 1,

2

RD Low to Data Valid

T

DDA

- -

4

T

CP

nS 1

Data Hold after RD High

T

DDH

0

-

2 T

CP

nS

Data Float after RD High

T

DDZ

0 -

2

T

CP

nS

RD Pulse Width

T

DRD

6 T

CP

-

∆ 6 T

CP

-

nS

2

Notes:

1. Data memory access time is 8 T

CP

.

2. "

∆" (due to buffer driving delay and wire loading) is 20 nS.

Data Write Cycle

PARAMETER SYMBOL

MIN.

TYP.

MAX.

UNIT

ALE Low to WR Low

T

DAW

3 T

CP

-

∆

-

3 T

CP+

∆

nS

Data Valid to WR Low

T

DAD

1 T

CP

-

∆

- - nS

Data Hold from WR High

T

DWD

1 T

CP

-

∆

- - nS

WR Pulse Width

T

DWR

6 T

CP

-

∆ 6 T

CP

-

nS

Note: "

∆" ( due to buffer driving delay and wire loading) is 20 nS.